# JOURNAL

April 1993

## JOURNAL

April 1993 Volume 44 • Number 2

## **Articles**

| 6  | A New Family of Microwave Signal Generators for the 1990s, by William W. Heinz, Ronald E. Pratt, and Peter H. Fisher                                                                                                     |  |  |  |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 12 | <b>Broadband Fundamental Frequency Synthesis from 2 to 20 GHz</b> , by Brian R. Short, Thomas L. Grisell, and Edward G. Cristal                                                                                          |  |  |  |  |

| 17 | A New High-Performance 0.01-to-20-GHz Synthesized Signal Generator Microwave Chain, by William D. Baumgartner, John S. Brenneman, John L. Imperato, Douglas A. Larson, Ricardo de Mello Peregrino, and Gregory A. Taylor |  |  |  |  |

| 27 | Internal Pulse Generator                                                                                                                                                                                                 |  |  |  |  |

| 30 | Concurrent Signal Generator Engineering and Manufacturing, by Christopher J. Bostak, Camala S. Kolseth, and Kevin G. Smith                                                                                               |  |  |  |  |

| 33 | A Design for Manufacturability, Design for Testability Checklist                                                                                                                                                         |  |  |  |  |

| 38 | A New Generation of Microwave Sweepers, by Alan R. Bloom, Jason A. Chodora, and James R. Zellers                                                                                                                         |  |  |  |  |

| 41 | Third-Order Curve-Fit Algorithm                                                                                                                                                                                          |  |  |  |  |

| 44 | A Digitally Corrected Fractional-N Synthesizer                                                                                                                                                                           |  |  |  |  |

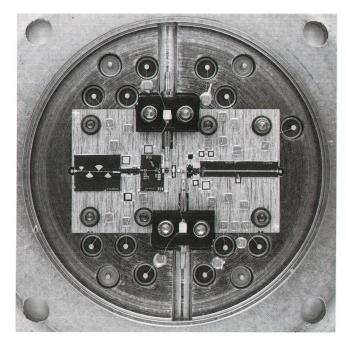

| 46 | Microcircuits for the HP 83750 Series Sweepers, by Eric V.V. Heyman, Rick R. James, and Roger R. Graeber                                                                                                                 |  |  |  |  |

Editor, Richard P. Dolan • Associate Editor, Charles L. Leath • Publication Production Manager, Susan E. Wright • Illustration, Renée D. Pighini Typography/Layout, Cindy Rubin • Test and Measurement Organization Liaison, Sidney C. Avey

Advisory Board, William W. Brown, Integrated Circuit Business Division, Santa Clara, California • Frank J. Calvillo, Greeley Storage Division, Greeley, Colorado • Harry Chou, Microwave Technology Division, Santa Rosa, California • Derek T. Dang, System Support Division, Mountain View, California • Bajesh Desai, Commercial Systems Division, Cupertino, California • Douglas Gennetten, Greeley Hardcopy Division, Greeley, Colorado • Gary Gordon, HP Laboratories, Palo Alto, California • Dim Grady, Waltham, Massachusetts • Matt J. Harline, Systems Technology Division, Roseville, California • Bryan Hoog, Lake Stevens Instrument Division, Everett, Washington • Roger L. Jungerman, Microwave Technology Division, Santa Rosa, California • Paula H. Kanarek, Inkjet Components Division, Corvallis, Oregon • Thomas F. Kraemer, Colorado Springs Division, Colorado Springs, Colorado • Ruby B. Lee, Networked Systems Group, Cupertino, California • Bill Lloyd, HP Laboratories Japan, Kawasaki, Japan • Alfred Maute, Waldbronn Analytical Division, Waldbronn, Germany • Michael P. Moore, VXI Systems Division, Loveland, Colorado • Shelley, L. Moore, San Diego, California • Dona L. Morrill, Worldwide Gustomer Support Division, Mountain View, California • Bill Lloyd, HP Laboratories Systems Software Division, Chelmsford, Massachusetts • Steven J. Narciso, VXI Systems Division, Loveland, Colorado • Garry Orsolini, Software Technology Division, Roseville, California • Bill Chronia • Garman • Marc Sabatella, Software Engineering Systems Division, Fort Collins, Colorado • Michael B. Saunders, Integrated Circuit Business Division, Corvallis, Oregon • Philip Stenton, HP Laboratories Bristol, Bristol, England • Beng-Hang Tay, Singapore • Stephen R. Undy, Systems Technology Division, Fort Collins, Colorado • Richard B. Wells, Disk Memory Division, Boise, Idaho • Lim Willis, Network and System Management Division, Fort Collins, Colorado • Kiichi Yanagawa, Kobe Instrument Division, Kobe, Japan • Dennis C. York, Corvallis Division, Corvallis, Oregon • B

| 52  | A Programmable 3-GHz Pulse Generator, by Hans-Jürgen Wagner                                                                                                               |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 56  | Pulse/Data Channel Extends Programmable Pulse Generator Applications, by Christoph<br>Kalkuhl                                                                             |  |  |  |

| 60  | <b>Design of a 3-GHz Pulse Generator,</b> by Peter Schinzel, Andreas Pfaff, Thomas Dippon,<br>Thomas Fischer, and Allan R. Armstrong                                      |  |  |  |

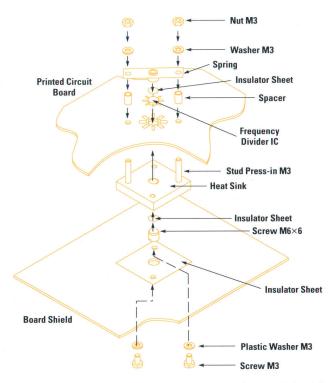

| 61  | Cooling of the Frequency Divider IC                                                                                                                                       |  |  |  |

| 73  | A Multirate Bank of Digital Bandpass Filters for Acoustic Applications, by James W. Waite                                                                                 |  |  |  |

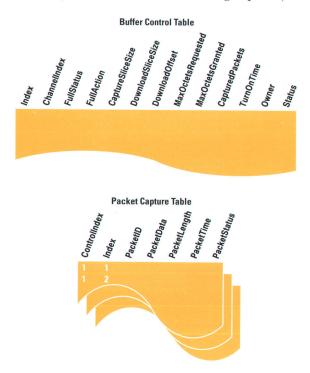

| 82  | Continuous Monitoring of Remote Networks: The RMON MIB, by Matthew J. Burdick                                                                                             |  |  |  |

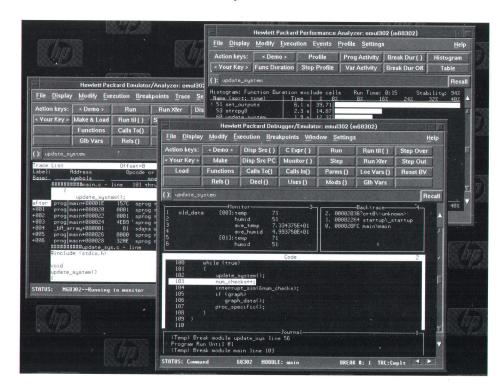

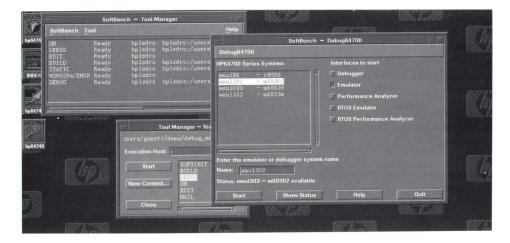

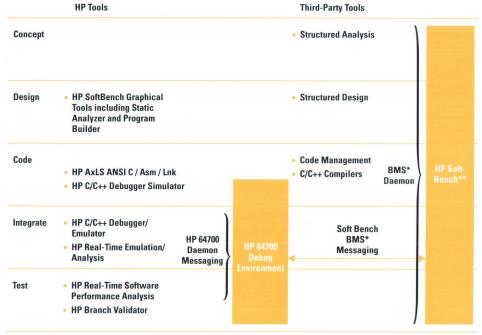

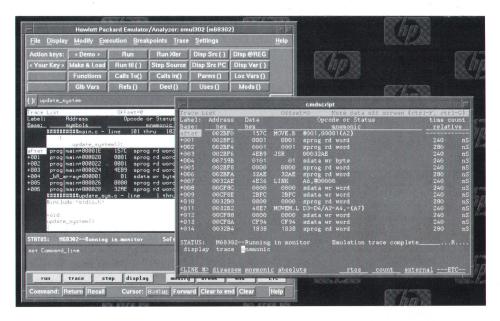

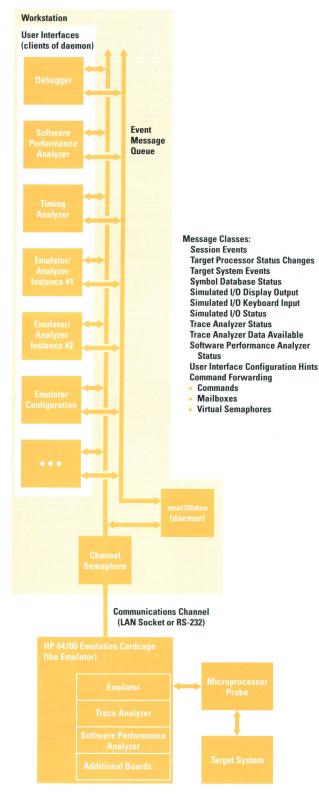

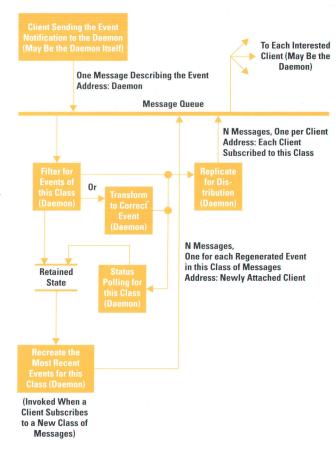

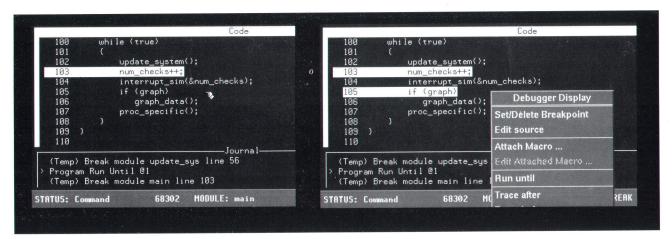

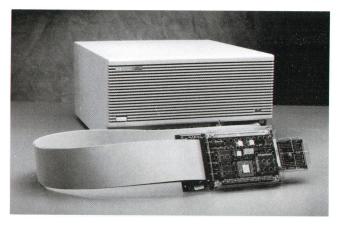

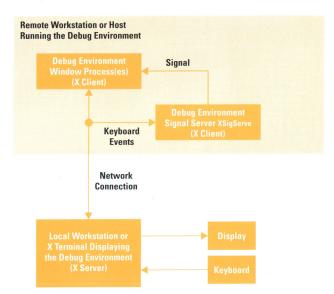

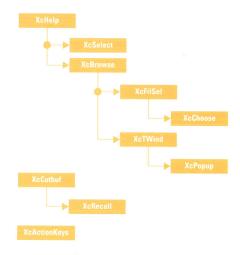

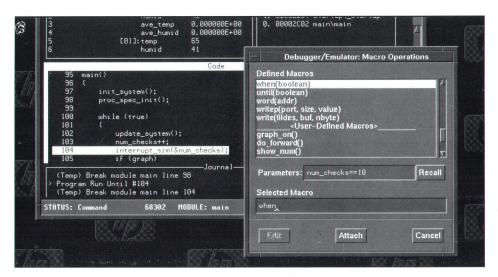

| 90  | The HP 64700 Embedded Debug Environment: A New Paradigm for Embedded System Integration and Debugging, by Robert D. Gronlund, Richard A. Nygaard Jr., and John T. Rasper. |  |  |  |

| 91  | The Value of Usability                                                                                                                                                    |  |  |  |

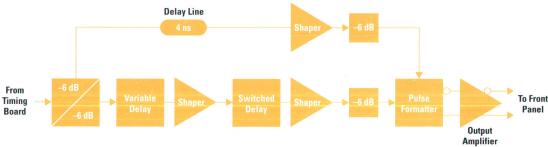

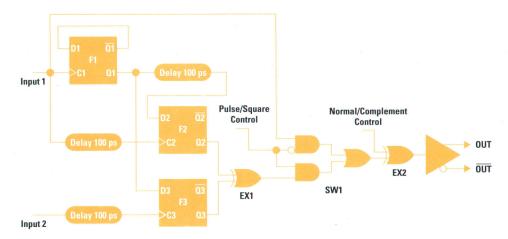

| 93  | The Debug Environment Connection to HP SoftBench                                                                                                                          |  |  |  |

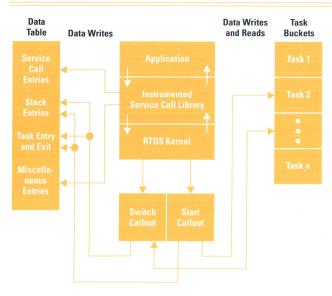

| 97  | A Real-Time Operating System Measurement Tool                                                                                                                             |  |  |  |

| 102 | A New Perspective on Emulation Hardware Modularity                                                                                                                        |  |  |  |

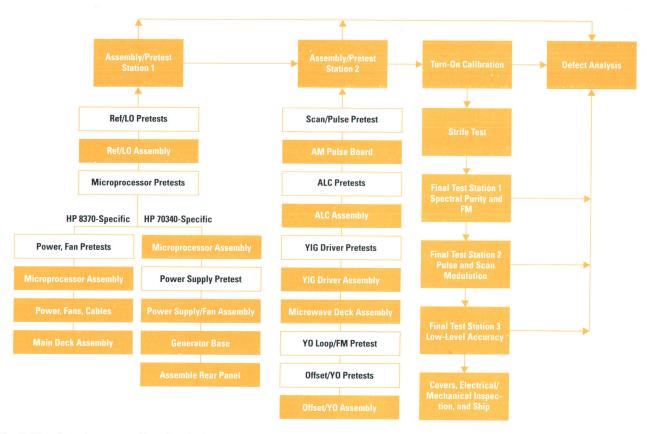

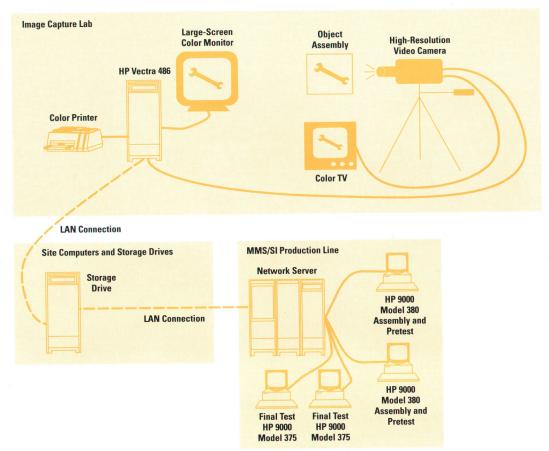

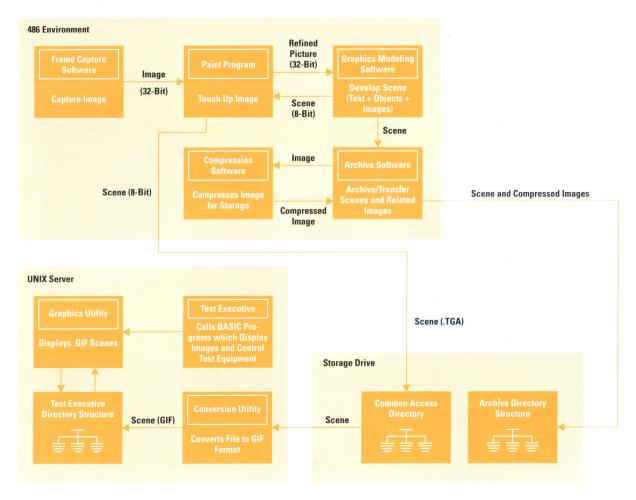

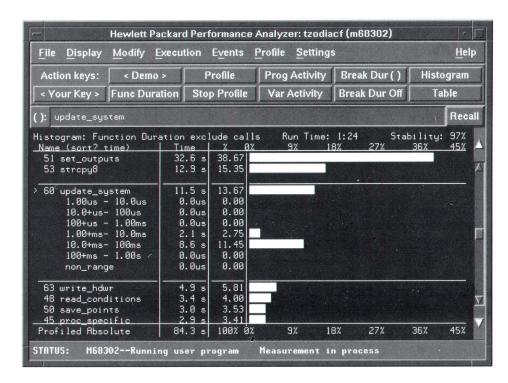

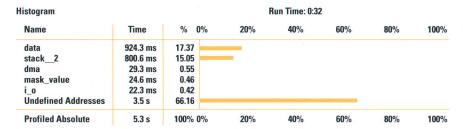

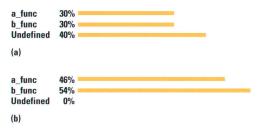

| 107 | Software Performance Analysis of Real-Time Embedded Systems, by Andrew J. Blasciak, David L. Neuder, and Arnold S. Berger                                                 |  |  |  |

|     |                                                                                                                                                                           |  |  |  |

## **Departments**

- 4 In this Issue

- 5 Cover

- 5 What's Ahead

- 116 Authors

The Hewlett-Packard Journal is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design and manufacturing engineering personnel, as well as to qualified non-HP individuals, libraries, and educational institutions. Please address subscription or change of address requests on printed letterhead (or 'include a business card) to the HP headquarters office in your country or to the HP address on the back cover. When submitting a change of address, please include your zip or postal code and a copy of your old label. Free subscriptions may not be available in all countries.

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HP-related research or solutions to technical problems made possible by using HP equipment are also considered for publication. Please contact the Editor before submitting such articles. Also, the Hewlett-Packard Journal encourages technical discussions of the topics presented in recent articles and may publish letters expected to be of interest to readers. Letters should be brief, and are subject to editing by HP.

Copyright © 1993 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies; and 3) a notice stating that the copying is by permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Editor, Hewlett-Packard Journal, 3200 Hillview Avenue, Palo Alto, CA 94304 U.S.A.

## In this Issue

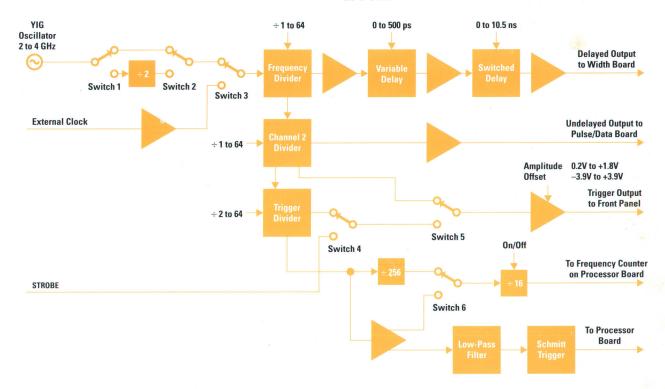

State-of-the-art designs for three traditional types of microwave signal sources—the synthesized signal generator, the sweep oscillator or sweeper, and the pulse generator—make up the bulk of this issue. All three are considered basic test equipment, the synthesized signal generator for receiver testing, the sweeper for component testing and general-purpose applications, and the pulse generator for digital device testing.

A signal generator provides a stable, low-noise output signal at a precise frequency and power level and offers flexible modulation capabilities. The article on page 6 introduces the new HP 8370 Series and HP 70340 Series synthesized signal generators, which have state-of-the-art performance in the frequency

range of 0.01 to 20 gigahertz. Key to their performance is a new architecture that uses two broadband fundamental oscillators instead of the oscillator and multipliers of previous designs, totally eliminating unwanted subharmonic frequencies. Details of the frequency synthesis section are in the article on page 12. The microwave chain, which divides the synthesized signal and provides for amplitude and pulse modulation, is described in the article on page 17. New processes developed for mixed-model, multiple-option production of these generators are detailed on page 30.

The HP 83750 Series sweepers (pages 38 and 46) produce swept-frequency output signals in the frequency range of 0.01 to 20 gigahertz. While previous designs locked the output frequency to a precise reference only at the beginning and end of each sweep in continuous-sweep mode, this new design ensures output frequency accuracy throughout fast analog sweeps. Like the signal generators with which they share this issue, these new sweepers use two broadband oscillators to generate their basic signal, eliminating multipliers and subharmonics.

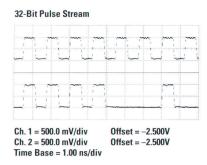

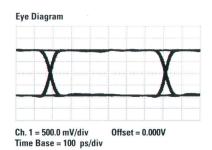

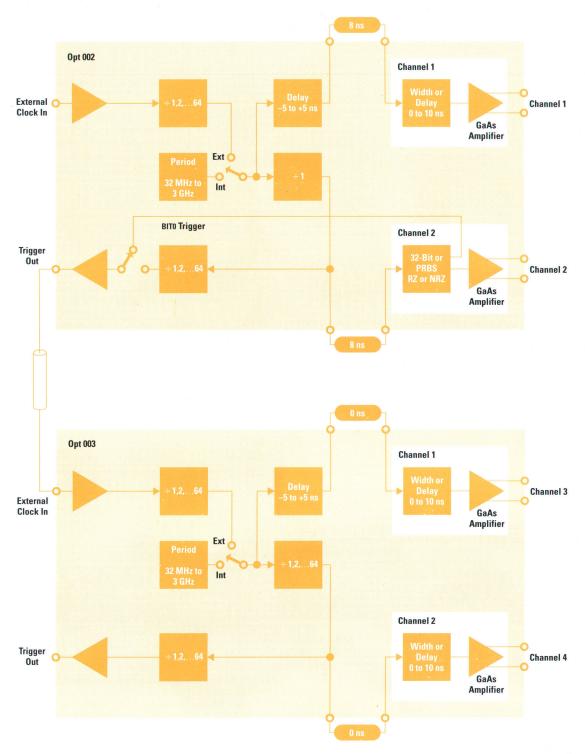

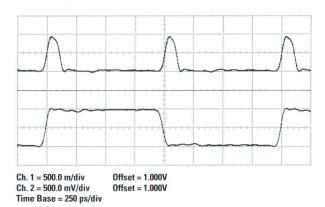

The HP 8133A pulse generator (pages 52, 56, and 60) offers pulse repetition rates to 3 gigahertz and extremely precise placement of the pulse edges to help resolve subtle timing and signal integrity problems in fast digital devices. Available configurations include a single pulse channel, two pulse channels, or a pulse channel and a programmable channel that generates data patterns or pseudorandom binary sequences. The design makes extensive use of hybrid microcircuits and custom integrated circuits.

Fundamental to the measurement of acoustic noise is the 1/3-octave real-time frequency analyzer. FFT (fast Fourier transform) analyzers are also useful for certain measurements. Taking advantage of recent increases in the speed of off-the-shelf digital signal processing chips, the HP 3569A real-time frequency analyzer provides in a single handheld package a dual-channel FFT analyzer, a real-time 1/3-octave sound intensity filter analyzer, an integrating sound level meter, and a reverberation time processor. The all-digital processing results in very high precision. The article on page 73 describes the HP 3569A, focusing on the design of its multirate bank of digital bandpass filters.

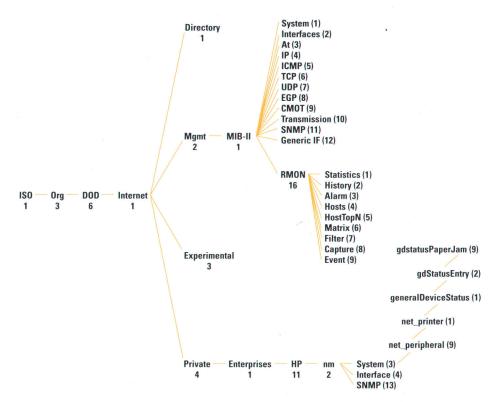

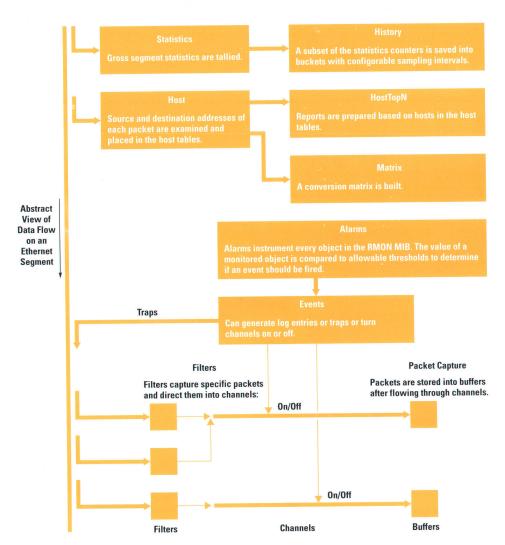

The Simple Network Management Protocol, a computer network management standard promulgated by the Internet Activities Board, has been widely accepted in today's open systems environment. Network monitors complying with this standard must gather network statistics according to one of the many Management Information Bases, some vendor-specific, that have been registered on the Internet. The HP LanProbe II network monitor implements the Remote Monitoring Management Information Base, which was developed by HP, Novell, ProTools, and other vendors and is enjoying growing support. The article on page 82 describes this Management Information Base and its implementation in the HP LanProbe II.

Unseen microprocessor-based systems are fundamental to the operation of many products not thought of as computers, such as microwave ovens and modern automobiles. Developers of such "embedded" systems need an extensive set of hardware and software tools to help them debug, analyze, and integrate these systems. The HP 64700 embedded debug environment (page 90) is designed to provide access to these tools with a single, easy-to-use, graphical user interface that conforms to the OSF/Motif standard. The debug environment offers a high-level language debugger, a real-time emulation control and state analysis interface, a real-time software performance analyzer interface (see page 107 for a discussion of the new software performance analyzer), and other tools, including a dynamic real-time operating system analysis tool. The debug environment can be used alone or integrated into an even more extensive set of software development tools under the HP SoftBench environment.

R.P. Dolan Editor

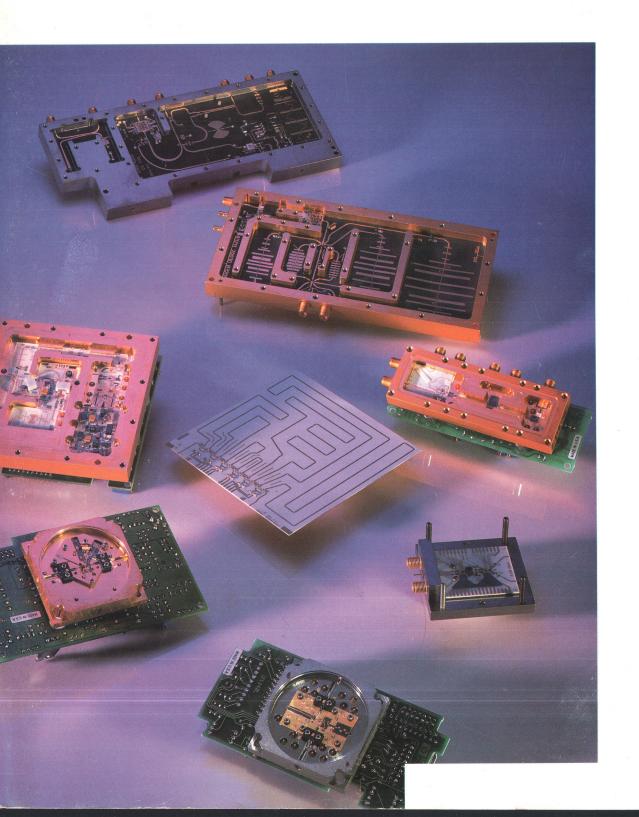

## Cover

The advanced microwave synthesized signal generators, sweep oscillators, and pulse generator featured in this issue depend on state-of-the art hybrid microcircuit technology for performance, reliability, and economy. On the cover, some of the microcircuits developed for these products pose for a group photograph.

## What's Ahead

The June issue will feature the HP ORCA system, a robot arm optimized for automating analytical laboratory tasks and other applications with similar needs. Also featured will be the HP Ultra VGA video adapter, the MPE/iX operating system, and HP's object-oriented database HP OpenODB. Finally, there will be six papers from the 1992 HP Software Engineering Productivity Conference—three are on practices for improving software quality, one on an error handling technique, one on configuration management for software tests, and one on a user interface development tool.

## A New Family of Microwave Signal Generators for the 1990s

This family of generators includes both stand-alone and modular versions. A new architecture and state-of-the-art technologies result in advanced performance.

by William W. Heinz, Ronald E. Pratt, and Peter H. Fisher

Microwave signal generators have been major products of the Hewlett-Packard Company over a time frame spanning five decades. In the 1950s, klystron signal generators such as the HP 618 and the HP 620 were providing calibrated signals covering major bands with convenient single-knob tuning and basic modulation capability for testing communications and radar receivers. The advent of backward-wave oscillator tubes in the 1960s led to microwave swept frequency sources that could be tuned electronically over octave bandwidths and provided efficient component test capability.

During the 1970s, solid-state YIG-tuned (yttrium iron garnet) oscillators and multipliers replaced the tubes, and with the incorporation of frequency synthesis techniques, new dimensions in frequency stability, accuracy, and spectral purity were realized over very broad bandwidths. Along with improved modulation, sweep capability, and programmability, these were the contributions of the HP 8672, 8673, and 8340 families of microwave sources, which set the standards for the 1980s. Major enhancements in performance and convenience were added later in the decade with the introduction of the HP 8360 family of synthesized sources.

Over the years, the needs of customers who use microwave sources have become more specialized. Manufacturers of wideband receivers must have generators with more modulation capability and wider frequency coverage, together with excellent spectral purity and a low broadband noise floor. People testing radars need low phase noise, accurate power output over a wide dynamic range, and flexible, accurate pulse modulation capability. Customers working in the communications industry need high-index frequency modulation and low phase noise, residual FM, and spurious frequency emissions. Other customers desire lighter weight and more compact packaging.

## **New Signal Generators**

The new HP 8370 and 70340 Series signal generators offer cost-effective solutions for these requirements as well as for other needs that can be anticipated for the 1990s. The HP 8370 Series includes not only signal generators for receiver test applications but also sweepers for component test and general-purpose applications. This article and the articles on pages 12, 17, and 30 discuss the design and manufacturing of the HP 8370 Series and HP 70340 Series signal generators. The sweeper members of the HP 8370 family are known as the HP 83750 Series, and are described in the articles on pages 38 and 46.

Six HP 8370 and 70340 signal generators have been introduced so far (see Table I). Four are in standard-rack-width, 5.25-inch-high packages and two are in Modular Measurement System (MMS) format.

| Microwave | <b>Signal</b> | Generator | Characteristics |

|-----------|---------------|-----------|-----------------|

| Model  | Frequency                       | Output            | Modulation           | Physical               |

|--------|---------------------------------|-------------------|----------------------|------------------------|

| Number | Range                           | Power             | Capability           |                        |

| 83731A | 1 to 20                         | –90 to            | Log AM,              | 5.25 in                |

|        | GHz                             | +10 dBm           | FM, Pulse            | high, 35 lb            |

| 83732A | 0.01 to 20                      | −90 to            | Log AM,              | 5.25 in                |

|        | GHz                             | +10 dBm           | FM, Pulse            | high, 35 lb            |

| 83711A | 1 to 20<br>GHz                  | −90 to<br>+10 dBm | CW Only              | 5.25 in<br>high, 35 lb |

| 83712A | 0.01 to 20<br>GHz               | −90 to<br>+10 dBm | CW Only              | 5.25 in<br>high, 35 lb |

| 70340A | 1 to 20                         | −90 to            | Log AM,              | 4/8-width              |

|        | GHz                             | +10 dBm           | FM, Pulse            | MMS, 19 lb             |

| 70341A | 0.01 to 1<br>GHz ex-<br>tension | −90 to<br>+13 dBm | Log AM,<br>FM, Pulse | 1/8-width<br>MMS, 5 lb |

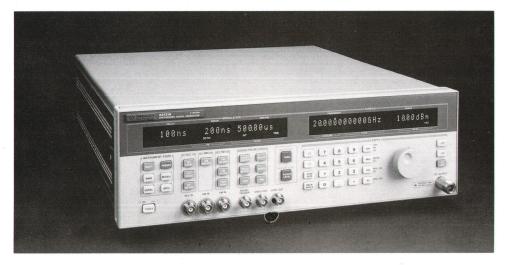

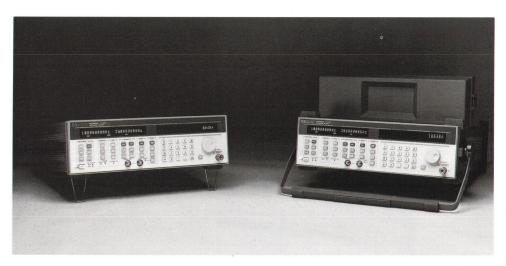

The HP 8370 Series represents the stand-alone members of the family. This series includes two signal generators provided with modulation capability optimized for receiver test applications. The HP 83731A (Fig. 1) covers the frequency range from 1 to 20 GHz, and the HP 83732A adds RF and IF test capability, covering the full 10-MHz-to-20-GHz range in a single, compact (17-inch-deep) package weighing less than 35 pounds, approximately half the weight of the previous generation of sources. Modulation capability includes highperformance pulse modulation (rise and fall times <10 ns and 80-dB on/off ratio). AM performance has been enhanced to provide logarithmic (-10 dB/volt) response down to -60 dB, suitable for antenna scan simulation and deep power sweeps for amplitude compression testing of receivers and subsystems. With the new wideband FM capability, modulation indexes exceeding 300 are possible.

The HP 83731A and 83732A feature a built-in pulse source that provides pulse rates from 3 Hz to 3 MHz and pulse widths from 25 ns to 419 ms. The pulse source can be selected from the front panel or an external controller. In triggered mode, delays of  $\pm419$  ms are available for pulse return

Fig. 1. The HP 83731A synthesized signal generator is representative of the stand-alone HP 8370 Series signal generators. This 1-to-20-GHz instrument has modulation capability optimized for receiver test applications.

simulation or other applications. In addition, there are pulse doublet and externally gated burst modes of operation, useful for receiver shadow-time measurements and simulating various real-world signals.

There are many measurement situations in which it is desirable to have the very accurate level calibration available at the front-panel RF connector of the signal generator transferred to a remote point in a system where lengths of cable or losses introduced after switch boxes have degraded the flatness of the signal. The user level correction feature allows this to be accomplished by connecting a power meter at the remote point with an HP-IB (IEEE 488) cable between it and the signal generator. The generator can control the power meter and store correction factors in memory (four tables can be stored with up to 401 points each). Calibrated, flat power levels then become available for accurate measurements at remote ports.

The other two signal generators of the HP 8370 Series are the HP 83711A and 83712A, which are CW sources designed for testing where an economical source without modulation capability is needed, such as in exciter and local oscillator applications. Sufficient power (+10 dBm) for mixer drive is provided with the same low harmonic levels (–55 dBc) as the versions with modulation.

## **Modular Versions**

There is a market segment that has requirements for instrumentation that equals the best in the industry along with reduced size and increased flexibility. To meet this need the significant contributions of the HP 8370 signal generators have been leveraged into the Modular Measurement System (MMS) platform (see Fig. 2). Supporting an optional modular display and adding an MSIB\* interface, the HP 70340A offers the same performance as its rack-and-stack counterpart, the HP 83731A, at half the size and two thirds the weight. A companion unit, the HP 70341A, is a one-slot MMS module that extends the HP 70340A's capability to cover the 0.01-to-20-GHz frequency range. The state-of-the-art accuracy of the HP 8370 Series signal generators is maintained in the modular versions by using the same overall architecture, which allows the modular products to be partitioned so that interchangeability of modules is achieved without any need for recalibration.

The HP 70341A frequency extension module contains 0.01-to-1-GHz dividers, amplifiers, modulators, and filters. Accurate power output is maintained by placing the low-frequency leveling detector inside the HP 70340A. This allows the frequency response characteristics of the 0.01-to-1-GHz path to be calibrated and stored in the nonvolatile memory of the HP 70340A. Correction factors for the nonlinearities of the pulse and scan modulators can be calibrated separately and stored in the nonvolatile memory provided in the HP 70341A.

Measurement Systems Interface Bus, the internal bus of the open standard Modular Measurement System.

**Fig. 2.** The HP 70340A signal generator is the Modular Measurement System version of the HP 83731A. The HP 70341A frequency extension module extends the range of the HP 70340A down to 10 MHz.

**Fig. 3.** An example of a modular measurement system consisting of an HP 70340A signal generator (highlighted) and an HP 71500A microwave transition analyzer.

This allows complete interchangeability of modules while maintaining the state-of-the-art specifications.

## **Measurement Systems**

In addition to reducing size and providing interchangeability of modules, the HP 70340A can work with other HP MMS products to create powerful, compact measurement systems. An example is illustrated in Fig. 3, which shows the HP 70340A and the HP 71500A microwave transition analyzer working together to obtain sophisticated data. Fig. 4 shows the HP 70340A being used with the HP 70841A pattern generator and the HP 70842A error performance analyzer to produce a compact, modular 3-gigabit bit error rate test system.

## **New Signal Generator Architecture**

To provide the improvements required for this new family of signal generators, a new architecture was implemented and technologies were incorporated that had matured only after

**Fig. 4.** A compact, modular 3-Gbit/s bit error rate test system consisting of the HP 70340A signal generator (highlighted), the HP 70841A pattern generator, and the HP 70842A error performance analyzer.

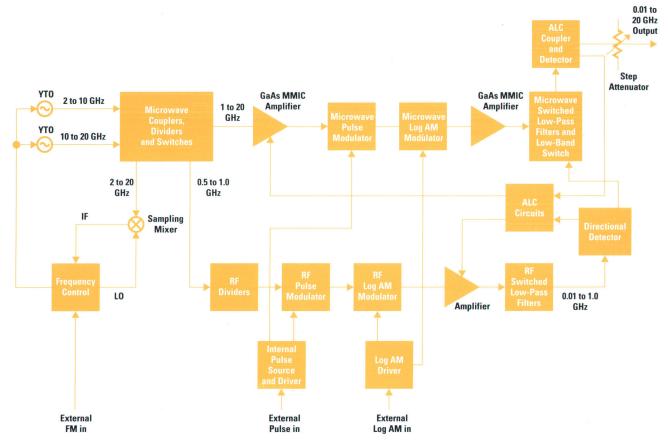

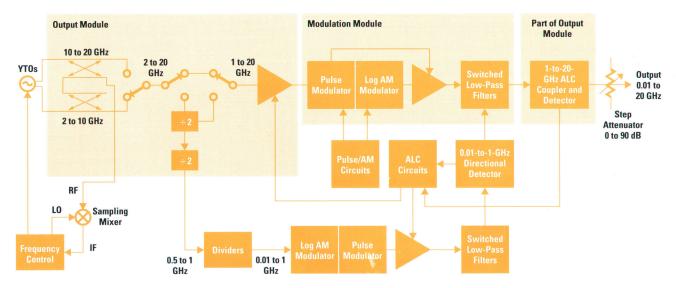

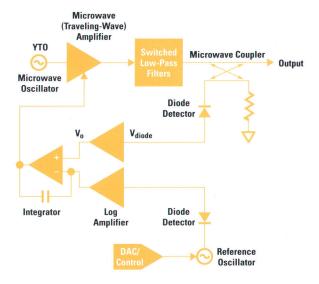

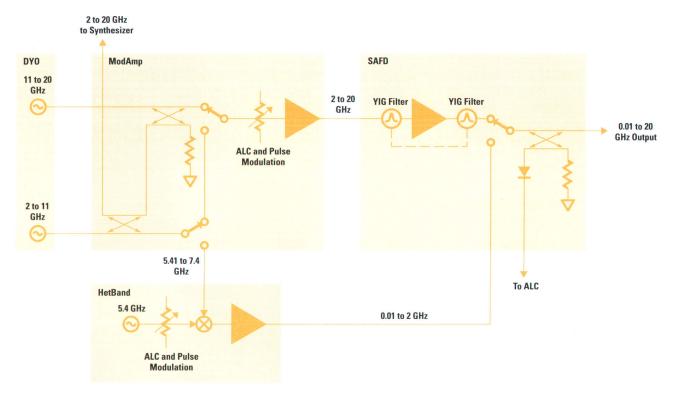

the previous generation of sources had been designed. A simplified block diagram is shown in Fig. 5. Two broadband YIG-tuned oscillators replace the YIG-tuned oscillator and multipliers employed in past designs and totally eliminate the generation of subharmonic frequencies. Broadband gallium arsenide (GaAs) monolithic microwave integrated circuits (MMICs) provide the gain, output power, and variable attenuation needed to develop the required signals. A bank of switched low-pass filters is used to attenuate unwanted harmonics without degrading the fidelity of the complex modulation placed on the carrier frequency.

Frequency extension below the 2-GHz lower limit of the YTO (YIG-tuned oscillator) is accomplished with microwave and RF frequency dividers, which cost less and provide higher performance than the previously used heterodyne low-frequency coverage. Precision, low-cost RF modulators implemented with surface mount technology complement their microwave counterparts.

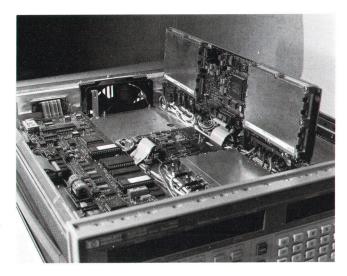

In addition to the use of GaAs MMICs, improvements in performance, cost, size, and weight have been attained through the high levels of integration achieved in the microwave chain by incorporating Duroid substrate technology to realize directional couplers, switches, filters, and interconnects. Previous reliance on multiple microcircuit packages connected together with coaxial cables has been supplanted by the use of just two integrated microcircuit subsystem packages.

The use of surface mount technology for the printed circuit boards provides a high degree of compactness and weight reduction compared to previous signal generators. In addition, the levels of performance required for the low-band (divider) frequency extension could not have been realized with the through-hole technology of the past.

## Leverage and Reuse

A high level of leveraging and commonality went into the design of the new family of signal generator products described here. The benefits of this approach extend to manufacturing as well, since economies of scale in fabrication, assembly, and test provide efficiency and savings. The microwave chain subassemblies are identical in the HP 83731A and 70340A. A simple replacement of the modulators within these microcircuits with 50-ohm transmission lines is the only change required to produce one of the CW signal generators of the HP 8370 Series. Even the power supply in the HP 8370 Series signal generators is common to all versions and is a self-contained, line-driven, switching unit. Four of the six major surface mount printed circuit board subassemblies in the HP 70340A are identical to the HP 8370 Series signal generator boards. The low-band divider board in the HP 70341A is identical to the low-band board in the HP 8370 Series signal generators. The power supply in the MMS version is driven by the standard 40-kHz, 24-volt power bus of the MMS mainframe.

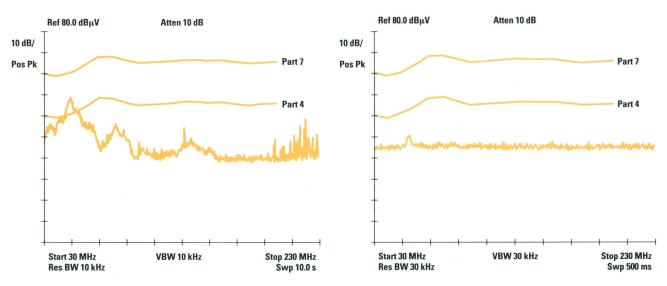

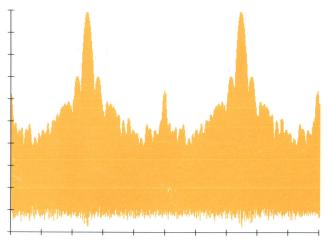

The Modular Measurement System standard has tight specifications for electromagnetic compatibility. Fig. 6 shows the initial results of emissions testing performed on the new family of sources. The modular source met specifications without any of the design modifications that were required to make the stand-alone products pass the test.

Fig. 5. Simplified block diagram of the new signal generator family. Two broadband oscillators replace the oscillator and multipliers of previous architectures.

The modular source can be placed in the same mainframe as the signal analyzer that was used to obtain the data presented in Fig. 6. This condition must not degrade the system performance. A test was devised that placed the HP 70340A in close proximity to a modular scalar network analyzer system that has a 140-dB dynamic range. Initial tests showed some degradation in network analyzer performance. This

was eliminated by connecting a 50-ohm load on the 0.5-to-1-GHz output of the signal generator and repairing a cracked solder joint on a coaxial cable. Retesting showed that the presence of the HP 70340A could not be detected by the wide-dynamic-range tracking generator system. Passing this test successfully is evidence of the EMI performance of the MMS platform.

Fig. 6. Initial radiated emissions test results for stand-alone (left) and modular (right) prototype signal generators. The modular unit met the specification while the stand-alone unit required further engineering. The limits shown are from MIL-STD 461B, RE 02.

Because of space constraints, the modulator drive circuits had to be squeezed onto the power supply board. These circuits already existed on boards that are specific to the HP 8370 signal generators. Since they were designed to fit into a standard cell, it was possible to leverage them for reuse in the HP 70340A. The microprocessor board is also specific to the HP 70340A, but is essentially an HP 8370 CPU board with the space used for the front-panel interface circuits on the stand-alone board occupied by the MSIB interface.

## **Firmware**

Another example of reuse is in the area of the firmware interfaces that exist between the hardware and the end user. Many instruments contain more computer power than was available in a small mainframe a decade ago. The firmware that controls this power has to be designed just as carefully as the microwave circuits. Reuse of firmware has played a key role in the development of this new family of signal generators.

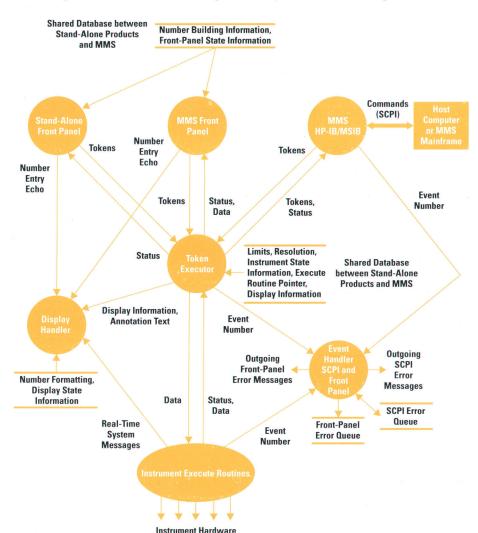

A greatly simplified model of the signal generator firmware is shown in Fig. 7, which indicates the major processes that must be controlled by the resident operating system when the instrument is in its normal mode of operation. All but one of these processes were reused from past efforts, so we

were able to concentrate on developing the instrument execution routines that are a major contributor to the high performance of the product family. The display handler, front-panel interface, and error handler processes were leveraged from the development efforts of several other products. A significant contribution was a hardware independent SCPI (Standard Commands for Programmable Instruments) parser supplied by HP's Instrument Controller Laboratory.

The front-panel processes share a common database that contains the requirements that are specific to each product. The token executor is a small process that receives and outputs standardized messages in the form of tokens. The operating system ensures that the tokens are processed in a sequential manner. A unique database for each instrument defines the actions of the token executor.

## **Low Cost of Ownership**

Each signal generator application has specific needs. The basic architecture of this new family of sources addresses a variety of these needs with an implementation yielding cost-effective solutions. Total cost of ownership is minimized by powerful internal verification capabilities, which can quickly isolate a fault to a given subassembly and reduce the mean time to repair to about four hours. The calculated mean time

Fig. 7. Overview of the HP 8370 Series and 70340 Series signal generator firmware. Six major processes are controlled by the resident operating system.

before failure is greater than 20,000 hours (about 10 years of normal use) and the recommended recalibration cycle has been extended to two years.

## Acknowledgments

Many of the people who contributed to the products described here are authors of other articles in this issue. Behind all of us is a large group of people who contributed to making the project a success. Tim Carey and Lynn Chroust provided key marketing support for the program and Al

Barber, as the project manager at the beginning of the project, made contributions to the definition and to the design. Ron Larson, Gary Rosen, and Ed Cirimele did a great job making the modular products a reality. Bob Skinner played a key role helping us apply surface mount technology to new, high-performance designs. Bill Wendin, Mark Johnston, and Paul Zander were instrumental in providing the firmware. Special thanks go to Bob DeVries and Phil Foster, who developed the product design concepts that made the entire product family a reality.

## Broadband Fundamental Frequency Synthesis from 2 to 20 GHz

A broadband fundamental YIG-tuned oscillator is locked to a stable reference and controlled by four phase-locked loops to produce the low-phase-noise output signal of the HP 8370 and 70340 signal generators.

by Brian R. Short, Thomas L. Grisell, and Edward G. Cristal

The frequency synthesis subsystem of the HP 8370 Series and HP 70340 Series synthesized signal generators produces a stable, accurate microwave carrier signal in the frequency range from 2 to 20 GHz and delivers it to the microwave subsystem, which is described in the article on page 17. Also, it is in the frequency synthesis subsection that frequency modulation is applied to the carrier.

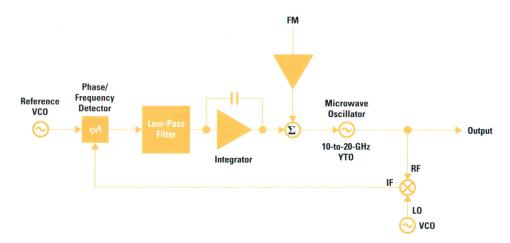

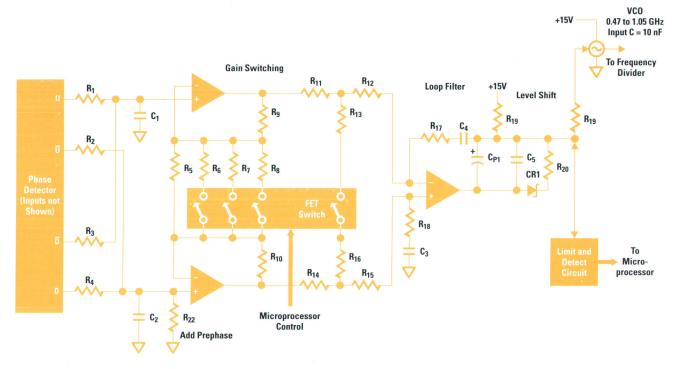

Fig. 1 is a simplified diagram of the microwave oscillator phase-locked loop used in the HP 8370 and HP 70340 signal generator families. Both VCOs in the diagram (the reference VCO and the LO) are locked to a common stable frequency reference (not shown in the figure). The phase/frequency detector outputs a voltage proportional to the phase difference between the reference VCO and IF frequencies, which after filtering and integration tunes the microwave YIG-tuned oscillator (YTO) in a direction to drive the phase difference error to zero.

Frequency modulation, when used, is summed into the forward path of the loop and simultaneously modulates the microwave oscillator together with the control signal. In dcFM mode the phase-locked loop is opened (the integrator nulled) and only the FM signal modulates the microwave oscillator.

## **Detailed Description**

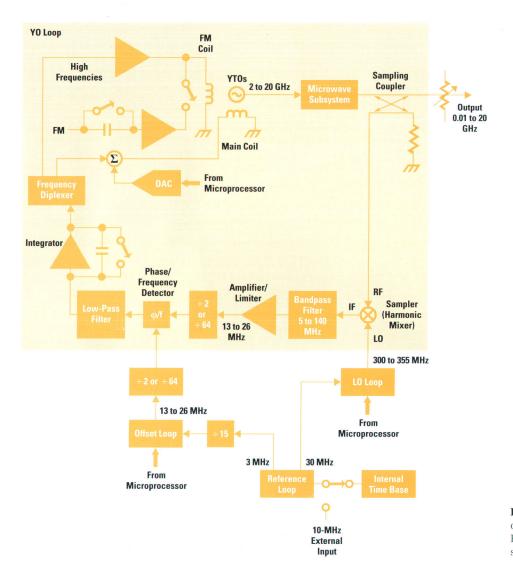

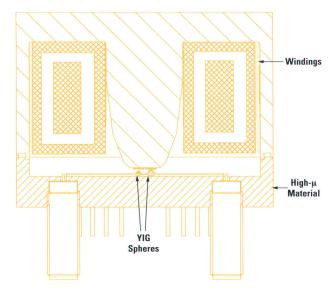

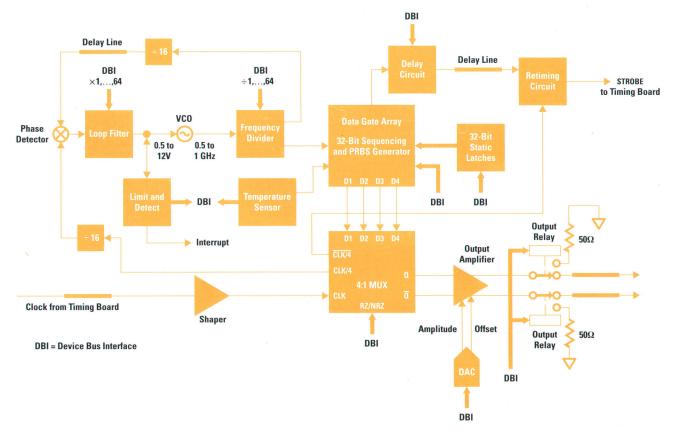

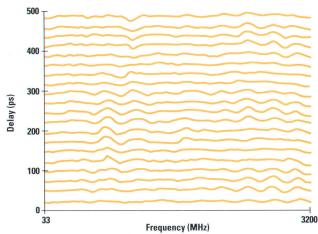

A more detailed drawing of the synthesis subsystem is shown in Fig. 2. The microwave oscillator is a pair of broadband

fundamental YIG-tuned oscillators covering 2 to 10 and 10 to 20 GHz. Each YTO relies on a high-Q yttrium iron garnet device whose resonant frequency is proportional to its internal magnetic field. The YTO tuning circuitry consists of two windings that control the magnetic field: a main coil, which carries the dc control current and sets the CW frequency, and a much smaller winding that has a broad frequency response, which is used for ac control and FM. The YTO system is locked to an internal 10-MHz frequency standard or to the user's external source by the phase-locked loop. Frequencies between 1 and 2 GHz are derived in the microwave subsystem by dividing the 2-to-4-GHz band. Frequencies between 10 MHz and 1 GHz are obtained by additional dividers located on the low-band subsystem printed circuit board. ALC (automatic level control), AM, and pulse modulation are added in the microwave subsystem.

The frequency synthesis subsystem consists of four phase-locked loops: the reference oscillator loop, the local oscillator loop (LO loop), the offset oscillator loop, and the microwave YIG oscillator loop (YO loop). The entire subsystem, excluding the sampler and the YIG oscillators, resides on three surface mount printed circuit boards. The main coil driver and its associated filters, amplifiers, and digital communication circuits reside on a 4-by-11-inch board. The YO loop, offset oscillator loop, FM driver, and associated digital communication circuitry reside on one 4-by-15-inch board, and the LO and reference oscillators and their associated

**Fig. 1.** Basic IF-type phase-locked loop used in the HP 8370 and 70340 Series signal generators.

**Fig. 2.** Block diagram of the frequency synthesis section of the HP 8370 Series and 70340 Series synthesized signal generators.

digital communication circuits reside on a second 4-by-15-inch board.

A quick trip around the YO loop in Fig. 2 shows its basic operation. A small amount of the YTO signal near the output of the instrument is sampled by a broadband transmission-line directional coupler and routed to the sampler, which acts as a harmonic mixer. The sampler, driven by the LO loop, produces a comb of harmonics which down-converts the microwave signal to the intermediate frequency (IF). The IF and extraneous mixing products are heavily filtered by the 5-to-140-MHz bandpass filter, then amplified, hard limited, and converted to digital pulses.

The digital signal is divided by 2, increasing the effective dynamic range of the phase/frequency detector, and becomes one of the two control signals used for phase comparison. The other control signal to the phase/frequency detector is generated in the offset oscillator loop. This loop provides the fine frequency resolution for the synthesizer.

The phase/frequency detector provides a net positive or negative voltage when the IF and offset oscillator frequencies are different. When the IF and offset oscillator signals have the same frequency, the detector produces a voltage proportional to their phase difference. In both situations, the integrated error voltage tunes the YIG oscillator frequency in a

direction to drive the error to zero. When the error voltage is zero, the YIG oscillator is phase-locked and remains locked because of the action of the integrator.

The error voltage from the integrator is frequency-diplexed so that higher-frequency components are routed to the low-inductance FM coil, while dc and lower-frequency components are transferred to the main coil. The frequency diplexer cutoff frequency is about 5 Hz.

## **Frequency Modulation**

Frequencies within the loop bandwidth of the YO phase-locked loop are tracked out by the action of the loop. Consequently, FM rates must exceed the YO loop bandwidth to modulate the YTO. To achieve the required FM bandwidth (1 kHz to 1 MHz in the HP 8370 Series) the YO loop bandwidth is reduced to about 600 Hz from its nominal 30 kHz. The high end is limited by the characteristics of the FM coil. Some gain and frequency equalization are added in the FM drive circuitry to flatten the overall response and provide a nominal 5-MHz/volt sensitivity and 600-ohm impedance at the front panel.

Also in FM mode, the dividers in front of the phase/frequency detector are switched to divide by 64. This further increases the detector's effective dynamic range, thereby allowing a

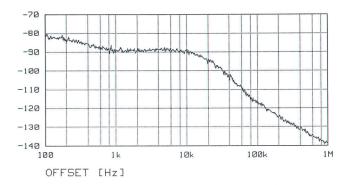

**Fig. 3.** Model 83731A phase noise performance at 9.999 GHz and  $\pm 10$  dBm.

large FM modulation index. The modulation index  $\beta$  is defined as the peak frequency deviation,  $\Delta f,$  divided by the modulation frequency,  $f_m.$  The phase/frequency detector is limited to  $\pm 2\pi$  radians, so we have the result:

$$\frac{\Delta f/64}{f_m} < \, 2\pi.$$

Rearranging factors gives:

$$\beta < 2\pi (64) = 402.$$

Because of practical limitations in the phase/frequency detector  $\beta$  is limited to around 300.

## **Phase Noise Performance**

As previously mentioned, the YO loop is able to track frequency variations within its bandwidth. This applies to noise as well. The largest noise contributors are the YTO, the LO, and the offset oscillators. The LO noise is increased by the harmonic factor of the sampler. The total phase noise at the output of the YO loop is the YTO phase noise reduced by the open-loop gain, plus the other loops' phase noise contributions. The noise contributions of the LO and offset oscillators are more significant within the YO loop bandwidth, and the YTO phase noise is the most significant outside of the YO loop bandwidth. The YO loop bandwidth is selected to be at the frequency at which the frequency-multiplied noise of the LO synthesizer and the free-run noise of the YTO are about equal. The noise contribution of the offset synthesizer is generally insignificant. A typical phase noise plot showing single-sideband phase noise as a function of offset frequency at 9.999 GHz and +10 dBm is shown in Fig. 3.

## Offset Loop

The offset loop is the phase-locked loop that sets the frequency resolution of the HP 8370 and 70340 Series signal generators. The offset loop output is phase-compared with

the sampler IF output (see Fig. 2). Therefore, the output frequency of the instrument changes by the same amount as any frequency change in the offset loop. The offset loop has an output frequency tuning range of 13 MHz to 26 MHz. Depending on the instrument option ordered, the frequency resolution can be either 1 Hz or 1 kHz.

The offset loop output signal drives the divide-by-2 or divide-by-64 circuit ahead of the YO loop phase detector. Because the offset loop is phase-compared with the output of the sampler, the spurious and phase noise performance of the offset loop translates directly to the output of the signal generator. Stated another way, the equation relating the output frequency of the offset loop to the output frequency of the entire instrument has no factors of frequency multiplication or frequency division. Therefore, given a desired set of spurious and phase noise specifications for the signal generator output, the corresponding specifications are required of the offset loop.

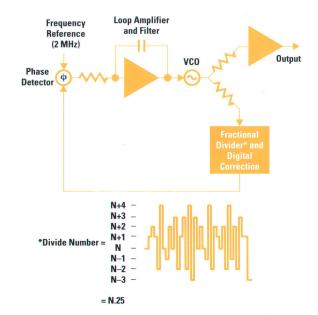

To obtain the frequency resolution required, the offset loop uses a fractional division scheme. A proprietary IC chip applies a digital correction technique using sigma-delta modulator technology and interpolative analog-to-digital conversion to shape the frequency spectrum of the fractional error energy. The shaping of the spectrum pushes the fractional error energy away from the carrier, where it can be filtered by manipulation of the loop response. The result is a fractional-N phase-locked loop that is not encumbered by the sophisticated error correction circuitry of past fractional-N phase-locked loops. The performance is high and the cost is low.

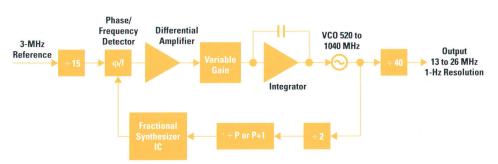

A basic block diagram of the offset loop is shown in Fig. 4. The VCO tunes from 520 MHz to 1040 MHz. This is a desirable frequency tuning range because the other reference loop, the LO loop, has a VCO that tunes from 300 MHz to 355 MHz. In any synthesizer, it is desirable not to have the internal phase-locked loops tuning over common frequency ranges. This is to minimize coupling between synthesizers, which could produce spurious responses. The output of the VCO is well-isolated from the dividers to prevent any spurious response from the VCO itself. The dividers include the output divider (divide by 40), and the prescaler ahead of the fractional synthesizer IC. The output of the fractional synthesizer IC is phase-compared with a 200-kHz reference signal. This reference is derived by dividing a 3-MHz external signal (traceable back to the 10-MHz crystal) by fifteen. The outputs of the phase detector are summed by a differential amplifier. At the output of the differential amplifier, a variablegain stage keeps the loop gain relatively constant. The VCO tuning constant varies over the tuning range, and the frequency division number from the VCO to the phase detector varies by a factor of 2 to 1. Both of these factors contribute

Fig. 4. Offset phase-locked loop.

Fig. 5. LO loop.

to reducing the loop gain at the high end of the output frequency range. The variable-gain stage compensates for these variations. The result is that the phase noise response of the loop remains relatively constant over the output frequency range. The variable-gain stage is followed in the loop by the loop integrator.

As previously mentioned, the spurious performance of the offset loop must be as good as the desired spurious performance of the signal generator output. The actual offset loop spurious performance is over 25 dB better than required. The phase noise performance required of the offset loop is also set by the desired signal generator phase noise specifications. The offset loop exceeds the desired phase noise performance at all offsets from the carrier by at least 30 dB. The divider at the output is the key to having so much margin in the spurious and phase noise performance. With frequency division at the output, the spurious responses and phase noise are improved by 20 times the logarithm of the division factor with respect to the carrier signal. In the offset loop the frequency division factor is 40, and the resulting improvement in noise and spurious performance is 32 dB.

The only other performance specification that affected the offset loop design was the switching speed. It was determined that to meet the instrument switching speed specifications, the offset loop must switch in less than 10 ms. To obtain this specification, the loop bandwidth was adjusted and a discharge path for the loop integrator capacitor was provided.

## **Microwave Sampler**

The HP 8370 Series uses a fundamental YIG oscillator to generate the output frequency directly, instead of multiplying the output from a lower-frequency oscillator. This requires that the microwave sampler be able to operate at the output frequency (as high as 20 GHz) to provide down-conversion for frequency control. The sampler used is borrowed from the HP 5350 Series microwave counters. It is received assembled and tested, and used as-is.

There are distortion mechanisms in the sampler that can cause spurious signal products at its output. Some of these, in turn, can cause undesired mixing products in the synthesis section and appear at the instrument output as spurious signals. An algorithm was used to search for the best sampler LO frequency for each microwave frequency to minimize spurious signals. These frequencies are stored in ROM in the HP 8370 Series and are used to set the LO and offset synthesizers appropriately for each output frequency band.

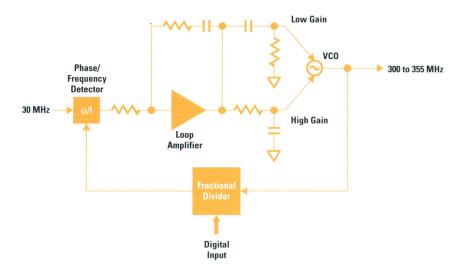

## LO Loop

As mentioned above, the LO loop output is one of the inputs to the microwave sampler. The LO loop, shown in Fig. 5, is a divide-by-N phase-locked loop with an output range of 300 to 355 MHz in 0.5-MHz steps. Phase noise performance of this loop is critical, since its output frequency is multiplied in the sampler to within an IF spacing of the YIG oscillator frequency. The multiplication can be as high as 66 times the LO frequency at 20 GHz, which increases the noise contribution by approximately 36 dB. Noise performance depends on careful VCO design, fractional division, and a low-noise reference.

The VCO is a cost-effective but high-performance printed circuit board varactor-tuned oscillator that uses a length of solid coaxial cable as the inductive element. This reduces the vibration sensitivity of the oscillator circuit because of the inherent self-shielding of the coax.

An important feature of this VCO is the presence of two tuning inputs: a low-sensitivity input and a high-sensitivity input. The phase-locked loop uses the high-sensitivity input to tune the VCO over the required frequency range. The low-sensitivity input has almost constant sensitivity in MHz/volt. This input is the one on which the loop bandwidth depends, so the bandwidth also remains constant. Constant bandwidth helps maintain optimum noise performance. The VCO phase noise is typically –122 dB/Hz at a 10-kHz offset.

Fractional division is used in the divide-by-N circuitry to aid low-noise performance. A straightforward way to achieve 0.5-MHz steps in frequency would be to use a 0.5-MHz reference and a divide-by-N divider. This, however, would cause a large multiplication of the reference noise. Instead, a 30-MHz reference is used, and the 0.5-MHz steps are developed by using a fractional divide-by-N circuit. Thus, noise is multiplied up by a much smaller factor: 0.5/30 or approximately 36 dB less than using a 0.5-MHz reference.

Fig. 6. Reference loop.

The fractional divider is realized using a combination of ECL digital circuits and TTL PAL (programmable array logic). It operates at 60 MHz.

The low-noise reference is provided by the reference loop, which is discussed below.

Much design work went into the whole instrument, and the LO loop in particular, to achieve excellent EMC (electromagnetic compatibility) performance. Again, one of the most difficult aspects was the large multiplication factor from the LO loop to the instrument output. Special internal shielding was developed for the VCO section on the printed circuit board to eliminate RF susceptibility of the VCO at its oscillation frequency, an important aspect to many users of microwave signal generators whose applications are in noisy RF environments that are rich in potentially interfering signals.

There are no adjustments in the LO loop.

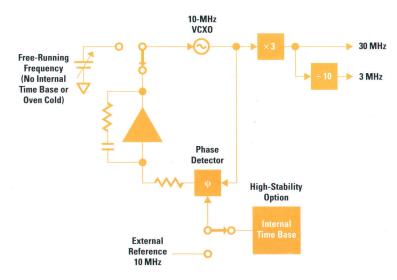

## Reference Loop

The reference loop, shown in Fig. 6, provides two references: 3 MHz for the offset loop and 30 MHz for the LO loop. It also allows the use of an external 10-MHz reference. The internal reference is a 10-MHz printed circuit board crystal oscillator, which is locked to either the external reference or the HP high-stability time base option if one is present. External references are automatically selected when present at the rear-panel connector, and the instrument microprocessor is notified for front-panel indication.

The printed circuit board crystal oscillator can lock over a range greater than  $\pm 500$  Hz and maintains a noise level of -155 dBc/Hz at 1-kHz offset at the 30-MHz output to the LO loop. There is one adjustment to set the unlocked frequency of the oscillator to account for crystal variations.

The 30-MHz output is developed by frequency-tripling the 10-MHz signal, and the 3-MHz output is derived from the 30-MHz output by a divide-by-ten digital divider.

An on-board detector senses an external reference and onboard logic disables the internal high-stability reference while switching the reference phase-locked loop input to the external reference port at the rear-panel connector.

## Digital and Analog I/O

Digital control and readback are done serially, using 16 bits. As a self-check, the serial bus is capable of reading back the data sent. It can also read status information from the LO loop. Unlock indications are handled by an interrupt system to avoid constant polling overhead for the instrument microprocessor.

Analog voltages and frequencies can be measured via a single-line analog bus that each board can drive using local analog multiplexers. Thus, power supplies, tune voltages, reference frequencies, and so on can be measured for troubleshooting and functional verification.

## Acknowledgments

We would like to acknowledge the contributions of Sunia Yang, Bill Cornelius, David Eagleton, and Terry Noe to the development of the synthesizer subsystem. Sunia designed the YO loop, Bill designed the YIG low-frequency driver, David characterized the YTO performance, and Terry designed the FM circuitry.

## References

- 1. B. Miller and R.J. Conley, "A Multiple Modulator Fractional Divider," *IEEE Transactions on Instrumentation and Measurement*, Vol. IM-40, no. 3, June 1991, pp. 578-583.

- S.R. Gibson, "Gallium Arsenide Lowers Cost and Improves Performance of Microwave Counters," *Hewlett-Packard Journal*, Vol. 37, no. 2, February 1986, pp. 4-10.

## A New High-Performance 0.01-to-20-GHz Synthesized Signal Generator Microwave Chain

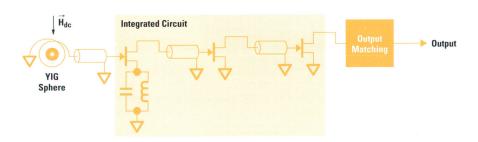

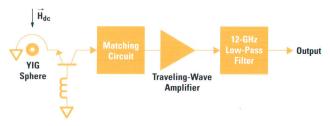

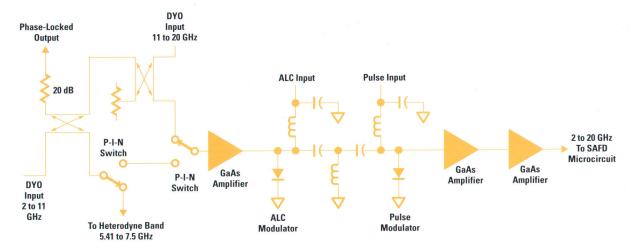

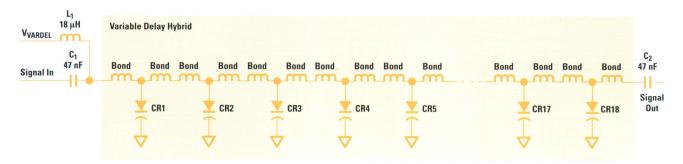

Driven by a broadband YIG oscillator, the microwave chain only divides the oscillator output instead of multiplying and heterodyning like previous designs. The benefits include no subharmonics and higher-performance pulse and amplitude modulation. The major functions of the microwave chain are integrated on two microcircuits.

by William D. Baumgartner, John S. Brenneman, John L. Imperato, Douglas A. Larson, Ricardo de Mello Peregrino, and Gregory A. Taylor

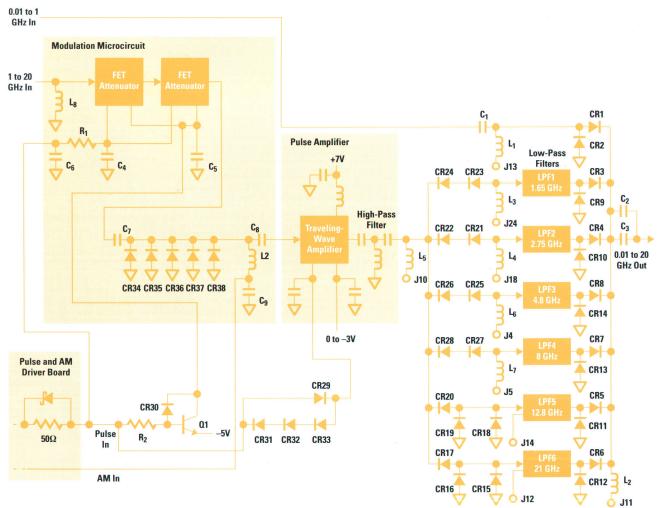

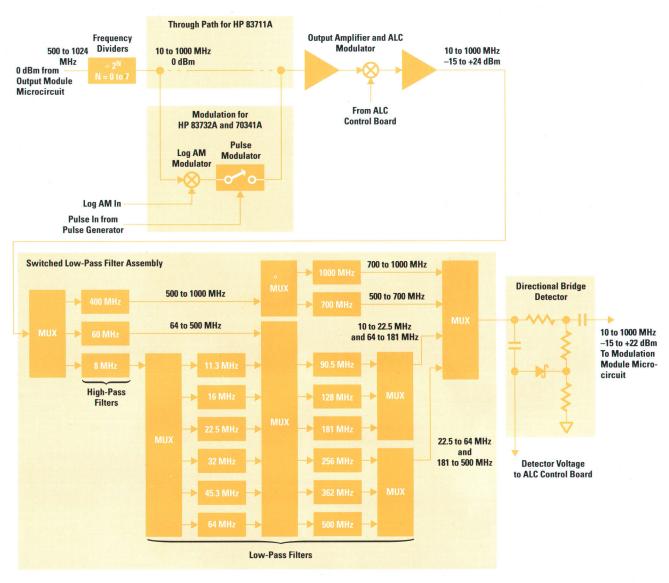

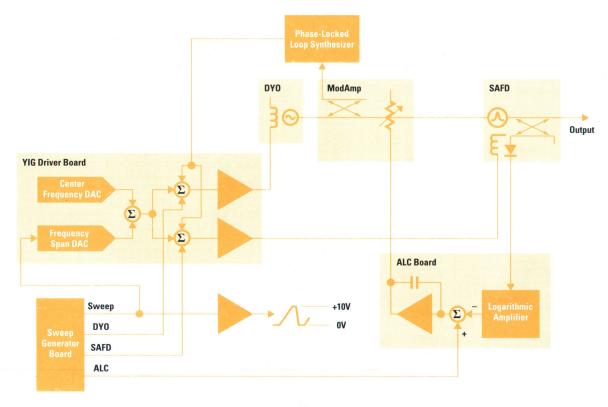

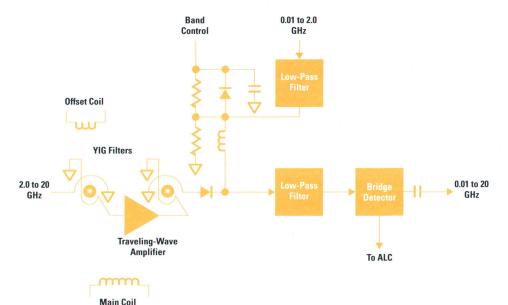

The microwave chain of the HP 8370 and HP 70340 synthesized signal generator families receives the output of the frequency synthesis section (2 to 20 GHz) and creates the leveled signal generator output signal (0.01 to 20 GHz).

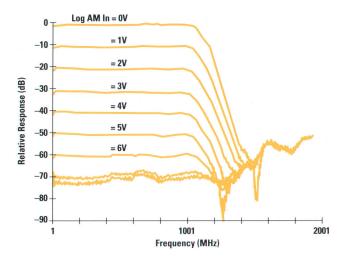

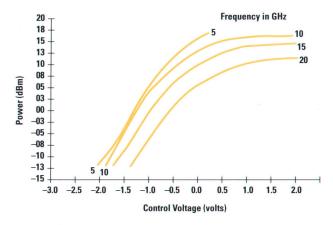

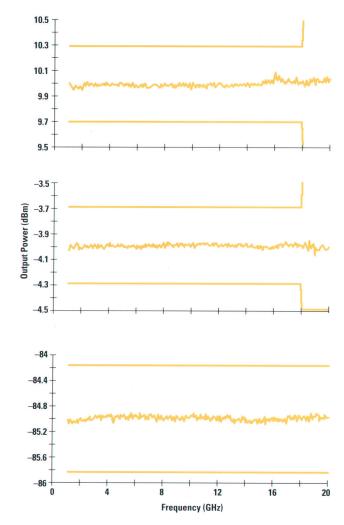

The evolution of the microwave chain was driven by the needs of receiver test and local oscillator customers for higher performance, and the desire to reduce size, weight, and cost. The key performance goals were +8-dBm output power, ±1-dB level accuracy, no subharmonics, low harmonics (–55 dBc), fast (10 ns) high-fidelity pulses, and the capability for simultaneous pulse and deep (–60 dBc) amplitude modulation to simulate rotating-antenna transmitters (Fig. 1).

Previous architectures start with a 2-to-6.6-GHz fundamental band, multiply to 26.5 GHz, and postfilter with a YIG (yttrium iron garnet) filter. The frequency control, ALC, AM, FM, and pulse modulation are situated in the fundamental band for lower cost. The disadvantages associated with this approach are subharmonics, low power, slow pulse rise time (25 ns) because of the narrow YIG filter, and slow AM response when the AM is simultaneous with pulse modulation.

$\label{Fig. 1.} \textbf{Rotating antenna spectrum is an example of simultaneous pulse and amplitude modulation.}$

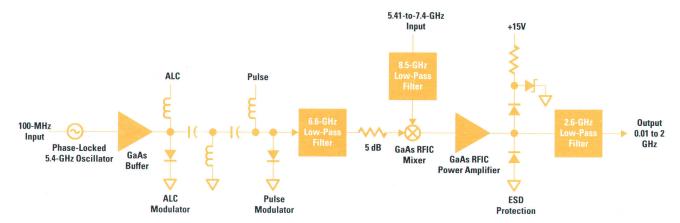

The HP 8370/70430 design takes advantage of new broadband gallium arsenide (GaAs) components to achieve the performance goals. Fig. 2 is a block diagram of the microwave chain. Subharmonics are eliminated by tuning a pair of broadband YIG-tuned oscillators (YTOs) over a 2-to-20-GHz range. Six low-pass filters reduce harmonics to less than –55 dBc. The low-pass filters have wide bandwidths, so they do not slow or distort pulses. Deep AM is linear in dB per volt and flatness with frequency is corrected to achieve –60-dBc depth. AM and pulse modulation can be used simultaneously.

Broadband noise in the output of a synthesized signal generator affects the sensitivity of a receiver under test and degrades noise figure meter accuracy when the signal generator is used as a local oscillator. In this design, AM noise is minimized by maintaining high power throughout the chain and not placing an amplifier at the output to boost power at the expense of noise. The YTO determines the AM noise at about 20 dB above the thermal noise level.

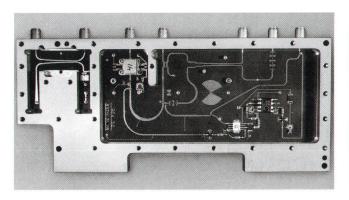

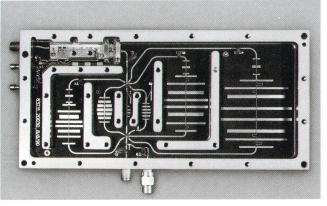

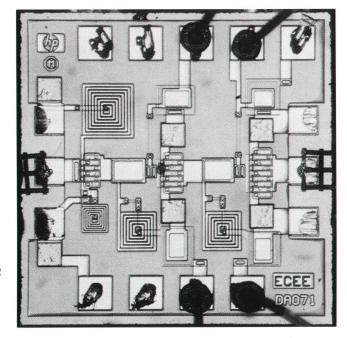

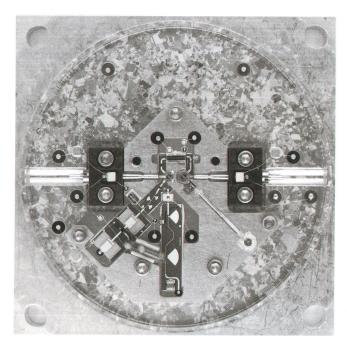

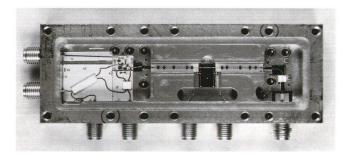

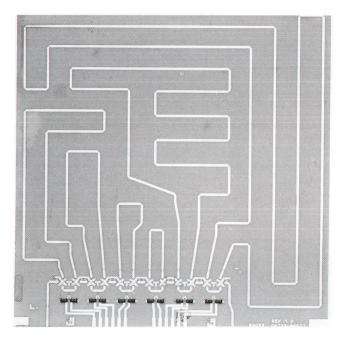

## **High Integration Level**

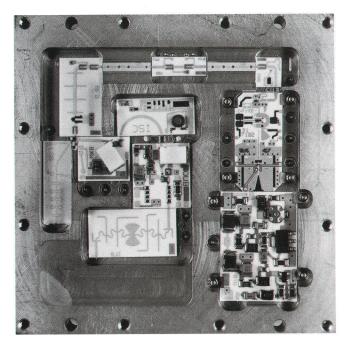

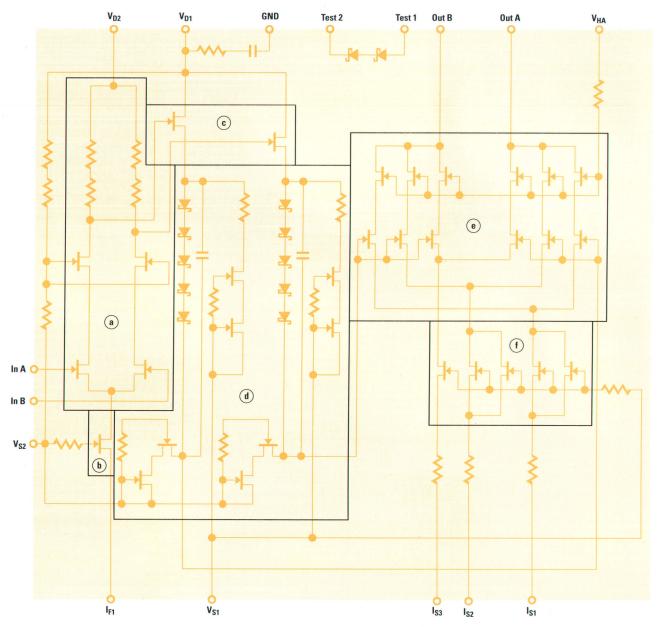

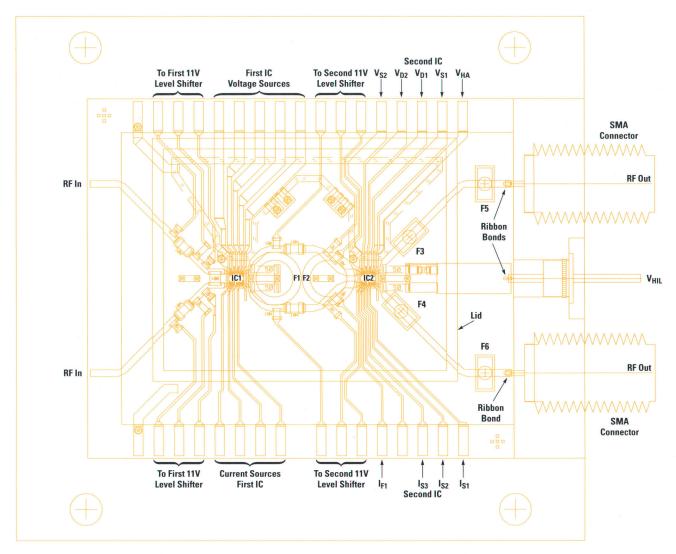

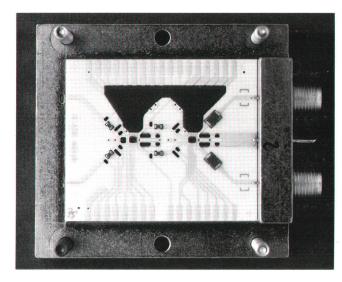

To lower cost while increasing performance, the circuits after the YTO are integrated on two principal microcircuits, called the output module (Fig. 3) and the modulation module (Fig. 4). This maximizes performance by eliminating transitions, connectors, and cables that add loss and mismatch. The circuits are fabricated on PTFE\*-based Duroid substrates and therefore can be relatively large without the circuit cracking encountered with both thick and thin films on hard substrates, which limits circuit sizes to about an inch or so. Both microcircuits are soldered into plated aluminum housings. To make it possible to use Duroid substrates with traditional chip and wire bonding, a bondable gold process was developed. Fabrication was simplified by careful tolerance analysis and the circuits are designed to eliminate RF adjustments, which can be costly. RF testing is done at the higher integration level. This improves yields over testing the lower-level circuits because a microcircuit can meet overall specifications and be accepted even

<sup>\*</sup> PTFE stands for polytetrafluoroethylene.

Fig. 2. Block diagram of the microwave chain of the HP 8370 and 70340 Series synthesized signal generators. Most of the microcircuits are integrated into two modules: the output module and the modulation module.

though one of its components may exhibit high loss and another low.

Further integration is achieved by using the amplifiers for more than one function. The first amplifier in Fig. 2, in addition to boosting power and buffering the YTO from AM frequency pulling, acts as the ALC modulator. The second amplifier is part of the pulse modulator.

## **Binary Dividers**

The use of binary frequency dividers to generate the 10-MHz-to-2-GHz band departs from the heterodyne systems used in previous broadband signal sources. The decision to replace the microwave mixers, oscillators, and amplifiers used in heterodyne down-converters with high-speed digital integrated circuits was driven by receiver test requirements for reduced noise, harmonics, and spurious signals. Advances in frequency dividers, broadband components for modulation and leveling, and high-density surface mount circuits for harmonic filtering make it possible to produce the divider system at a much lower cost than heterodyne systems of equivalent performance.

Heterodyning a section of the microwave band to the 10-MHz-to-2-GHz spectrum involves design compromises. Mixers used in the frequency translation inherently generate inband spurious signals. Drive levels to the mixer are reduced

to minimize these spurs, decreasing the signal-to-noise ratio at the mixer output. Amplification used to bring the signal up to required levels raises the broadband noise floor as well. The mixing process duplicates the microwave phase noise characteristics in the RF band. Frequency division avoids these problems. Phase noise and spurious signals are reduced 6 dB with each octave of division. For a 70-MHz signal this results in a 36-dB improvement over heterodyne systems. The dividers handle moderate power levels and result in noise-floor improvements up to 20 dB.

Frequency division introduces some different design constraints. Output waveforms are square waves with a very rich harmonic spectrum. Third harmonics are only 9.5 dB below the fundamental and even-order harmonics, theoretically suppressed, require filtering. The harmonic specification of -55 dBc required filtering after the final amplification stages. Increased filtering to remove divider harmonics was added to the low pass-filter structures at minimal increase in product cost.

The modular nature of the cascaded dividers allowed low-cost frequency extension of the multifunction microcircuits from the 2-GHz low end of the YTO down to 1 GHz. Signal conditioning in the 1-to-2-GHz range is most economically

Fig. 3. Output module.

Fig. 4. Modulation module.

done with the distributed components in the microcircuits. The extra octave allows the base source to supply the bands in the 1-to-2-GHz range, which used to require several generators or a complete heterodyne system. Surface mount technology provides repeatable RF performance for lumped-element design of the 10-MHz-to-1-GHz band.

Level accuracy is achieved by a ratioing ALC loop that is accurate over level and temperature and is corrected for power flatness variation over frequency.

## **Output Module**

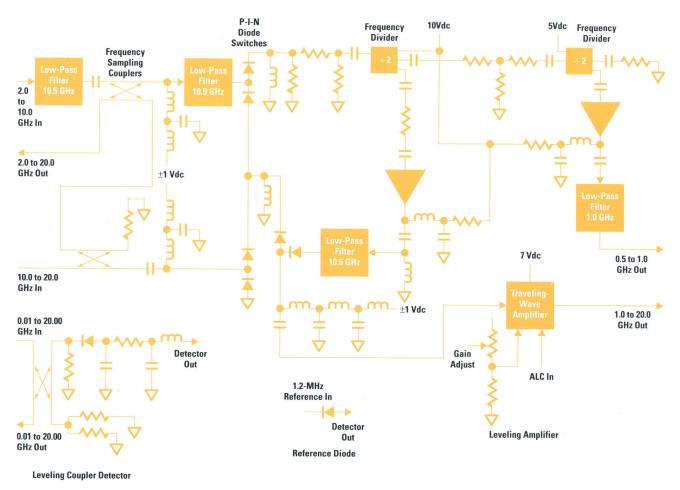

The first of the two multifunction microcircuits, the output module (Fig. 5), performs four functions. The first function is to couple a portion of the oscillator output back to the frequency sampler and the frequency control subsystem. Two directional couplers, each covering a YIG-oscillator frequency band, were designed for this purpose.

The second function of the output module is to provide switching to route the microwave signal from the appropriate YIG oscillator band through the microwave chain. Thirdly, the output module divides the YIG oscillator output in the 2-to-4-GHz range by two or four to generate signals from 0.5 to 1.0 GHz and 1.0 to 2.0 GHz. The 0.5-to-1.0-GHz band is used to drive the low-band circuit board, which generates outputs in the 0.01-to-1.0-GHz range.

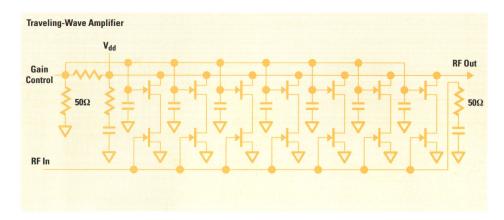

The fourth function of the output module is microwave signal processing for the automatic level control (ALC) subsystem. A broadband directional coupler detector samples the average power incident on the synthesizer load and feeds back the sample to the level control loop circuitry. The variable-gain traveling-wave amplifier acts as the leveling loop control element, modulating the microwave power to the desired level.

A PTFE-based material, RT/Duroid 5880, was chosen as the substrate for the output module. This material has a low loss tangent (0.0009 at 10 GHz), can be processed in a printed circuit board shop (resulting in low cost), and can be used for large circuits that have complex outlines (unlike a large piece of alumina, which will crack when subjected to thermal stresses after being been laser-routed into a complicated shape).

Extensive use was made of CAD tools in the development of the components that are integrated into the output module. These tools included linear circuit simulators, system simulators, and graphical layout tools. One extremely useful program, written by Jeff Meyer of HP's Systems Solutions Division, computes the solution of Laplace's equation in a two-dimensional region. The program uses the method of moments to solve for the Laplacian potential. Properties of unconventional transmission line structures can be analyzed

Fig. 5. Block diagram of the output module.

Fig. 6. Printed ground return with shunt stub in a diode switch circuit.

with the help of this program, and as a result, it was possible to design circuits not realizable with ordinary microstrip transmission line.

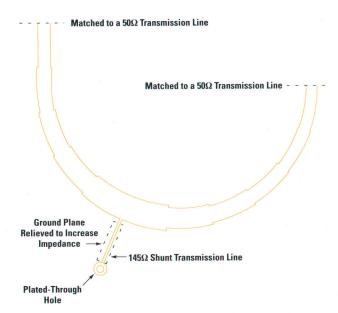

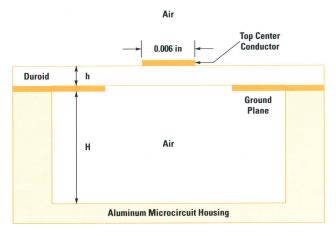

Switching in the output module is done with p-i-n beam-lead diodes. Two switches cover the 1-to-20-GHz frequency range. One is a double-pole, double-throw switch and the other is a single-pole, double-throw switch. It was a design goal to use as many printed components as possible to lower the assembly cost and ensure repeatable performance from unit to unit. The printed ground return shown in Fig. 6 provides a dc short while passing microwave signals from 2 to 20 GHz with a minimum of 20 dB return loss. The method of moments field solver program was used to design the 145-ohm characteristic impedance shunt stub in this circuit. Since the maximum impedance achievable with a microstrip transmission line on a 0.010-inch-thick RT/Duroid 5880 substrate is 110 ohms, it was necessary to modify the structure by etching the gap in the ground plane as shown in Fig. 7. The field solver was used to calculate the gap width required to achieve 145 ohms for a fixed top conductor width of 0.006 inch. By making H>h, the transmission line impedance was

Fig. 7. Cross section of 145-ohm shunt stub.

Fig. 8. Leveling coupler detector frequency response.

made insensitive to manufacturing variations in the housing dimensions and in the circuit attach process.

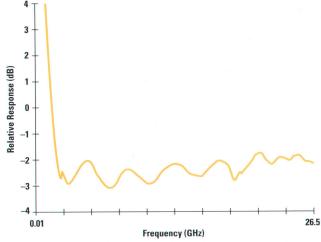

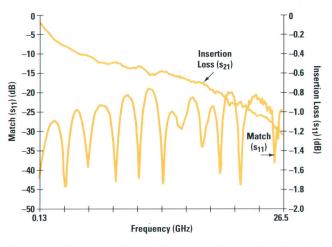

The leveling coupler is an asymmetric, continuously tapered, parallel-line coupler. The nominal coupling is 20 dB from 2 to 20 GHz. An RT/Duroid 5880 overlay, clamped in place with a silicone sponge-rubber pad, is used to equalize the even-mode and odd-mode velocities. The method of moments field solver was used to design this structure by generating a table of odd-mode impedance values versus coupling gap. This table was used to synthesize a design using ideal coupled transmission lines. The directivity of the coupler is typically better than 16 dB to 20 GHz. Good directivity in the leveling coupler results in a good source match and output level accuracy for the signal generator. The overlay and sponge clamp are thick enough so that currents are not induced in the package lid above the coupler. This allows a smooth transition to conventional microstrip. A broadband microstrip detector using planar doped barrier beam-lead diodes is therefore easily integrated with the coupler into a single housing. Integrating the leveling coupler detector with other circuits into one module yields substantial cost savings relative to previous signal generator block diagrams in which the coupler was a connectorized component purchased from an outside vendor and the detector was separately housed in an expensive package. The integrated design also allows the addition of a reference diode for temperature compensation. Figs. 8 and 9 show typical performance for the coupler detector.

Two additional microstrip couplers in the output module cover the 2-to-10-GHz and 10-to-20-GHz frequency bands. These couplers are used to feed back the signals from the frequency synthesis section to a frequency sampler. The construction of the 2-to-10-GHz coupler is similar to that of the leveling coupler. Its coupling ratio is 20 dB at 2 GHz and rolls off at 6 dB per octave to 10 GHz. The coupler was designed this way to reduce the level of harmonics incident on the frequency sampler. The 10-to-20-GHz coupler is entirely planar, making it very inexpensive to manufacture. It is a three-section, symmetric coupler with a nominal 33-dB coupling ratio. The even and odd modes are equalized by a printed capacitor at each end of the center section.

Fig. 9. Leveling coupler/detector insertion and return loss (match).

The broadband traveling-wave amplifier (described later) is housed in a hermetically sealed, ceramic package. This ensures reliable performance of this GaAs integrated circuit over varied environmental conditions such as high humidity and temperature. Careful engineering ensures that the ceramic package does not degrade the microwave performance of the traveling-wave amplifier chip to 20 GHz.

Two static frequency dividers generate the 1-to-2-GHz band, which is switched back into the 1-to-20-GHz path, and the 0.5-to-1-GHz output drive for the 0.01-to-1-GHz divider band.

## **Modulation Module**

The functions of the second microcircuit, the modulation module, include pulse modulation, amplitude modulation, and harmonic filtering, all from 1 to 20 GHz. This module also contains a low-distortion combining switch for the 0.01-to-1-GHz band. The modulation is implemented with a 0.010-inch thin-film alumina circuit on a 0.015-inch molybdenum carrier for thermal expansion matching and a hermetic thick-film alumina-packaged traveling-wave amplifier. The harmonic filtering and broadband combining switch are implemented on a 0.010-inch Duroid substrate. Fig. 10 is a diagram of the modulation module.

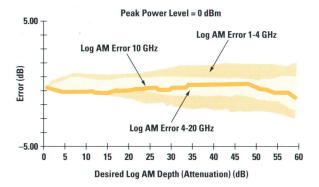

AM for the instrument is provided by a modulator containing five shunt p-i-n diodes. <sup>1</sup> Originally designed for pulse modulation, in this case the modulator is used to provide 60 dB of logarithmic AM. The transfer function of the AM modulator is corrected as a function of modulation depth and frequency with gain and offset DAC (digital-to-analog converter) adjustments. Fig. 11 shows the deviation from linearity as a function of depth and frequency. The driving function departs

Fig. 10. Block diagram of the modulation module.

Fig. 11. Typical log AM error (deviation from desired depth) at  $25^{\circ}$ C for carrier frequencies between 1.0 and 20 GHz.

from traditional AM in that it is logarithmic  $(-10~\mathrm{dB/V})$ . The log driving function is ideal for simulating large dynamic ranges like the deep nulls in an antenna scan pattern.

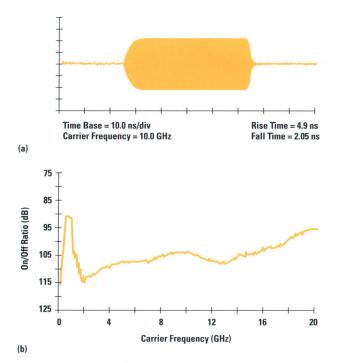

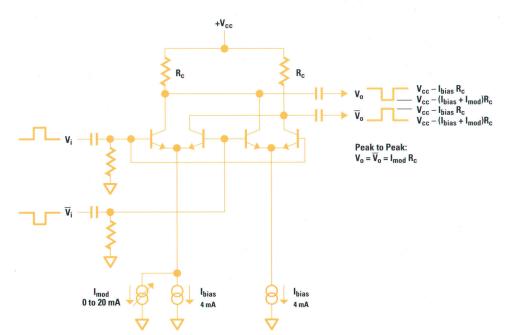

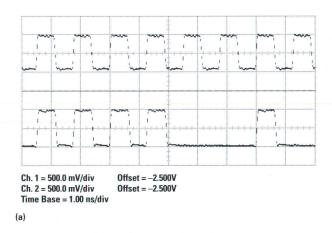

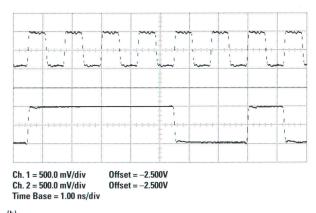

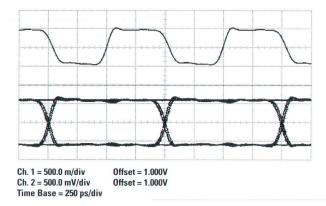

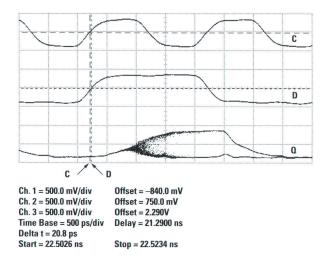

Pulse modulation for the instrument is implemented with three GaAs ICs: two attenuators and one traveling-wave amplifier. Specifications include 10%-to-90% pulse rise and fall times less than 10 ns, pulse on/off ratio  $>\!80$  dB,  $<\!10\%$  pulse overshoot,  $\pm 1$ -dB pulse level accuracy (relative to the CW level), and  $<\!20\text{-mV}$  peak-to-peak video feedthrough. Fig. 12 shows a typical pulse and a typical pulse on/off ratio plot.

**Attenuators.** The attenuators are series-shunt-series attenuators (Fig. 13). The series elements are common-gate FETs with 50-ohm resistors connected in parallel from drain to source. The shunt element is composed of four commongate FETs connected in parallel with some transmission line spacing between them. This spacing contributes to a good

Fig. 12. (a) Typical pulse modulation envelope. (b) Typical pulse modulation on/off ratio at  $+8~\mathrm{dBm}$ .

Fig. 13. FET attenuator.

match. It also results in a lower on/off ratio at low frequencies, where the spacing is negligible compared to a wavelength. The gates of the shunt FETs are driven by signals that are complementary to those that drive the gates of the series FETs. In the on state the series FETs are on and the shunt FETs are off, allowing the signal to pass. In the off state the series FETs are off and the shunt FETs are on, thus connecting the 50-ohm resistors that are in parallel with the series FETs to ground through the shunt FETs. This maintains a good match in the off state, unlike p-i-n diode modulators. This preservation of match in both states contributes to the good pulse envelope fidelity.

Amplifier. The traveling-wave amplifier is a seven-stage cascode design (Fig. 14). The gates of the common-gate FETs of the cascode are used to control the amplifier gain. In the on state, this control is high and the amplifier provides about 6 dB of gain. In the off state, this control is low, pinching off the FETs and turning the amplifier off. In this way the amplifier contributes to the pulse on/off ratio. The frequency response is dominated by the gate-to-source capacitance of the common-source FETs, so the on/off ratio is lower at higher frequencies. The traveling-wave amplifier thus complements the attenuators, compensating for loss and on/off ratio frequency response. Also, the match of the traveling-wave amplifier is maintained in both the on and off states.

**Pulse Performance**. Other factors that affect pulse on/off ratio are leakages and waveguide modes. The main leakage path is through the gate of the first series FET of the first attenuator, through the bias circuitry, and into the traveling-wave amplifier control. Bypassing is required to reduce this leakage to acceptable levels. Waveguide modes are suppressed with polyiron and narrow channels in the housing.

The pulse level accuracy is dominated by thermal effects in the traveling-wave amplifier. In the off condition, the amplifier cools down. When it is turned on, the gain is initially higher and drops as the traveling-wave amplifier heats up, with a time constant on the order of 10  $\mu s$ . Pulse level changes are typically about +0.5 dB from CW levels.

The pulse rise and fall times are dominated by the travelingwave amplifier switching time. The bypassing element

Fig. 14. Traveling-wave amplifier.

requirements impose a lower limit on capacitance at the traveling-wave amplifier control input. Also, there are internal capacitors on each of the seven stages' second gates. The drive source impedance is nonlinear: the off-state impedance is low, and the on-state impedance is 50 ohms. A low impedance for the off state provides quick discharging of the bypass capacitance, and the matched impedance for the on state maintains good pulse envelope fidelity (a low-impedance driver in both states would cause pulse overshoot and ringing). The driver used is simply a low-source-impedance circuit with a 50-ohm series output resistor and a Schottky diode in parallel with the 50 ohms (Fig. 10). For signal generator models without AM and pulse modulation the carrier circuit is replaced by a through line on a Duroid substrate.

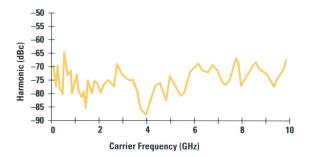

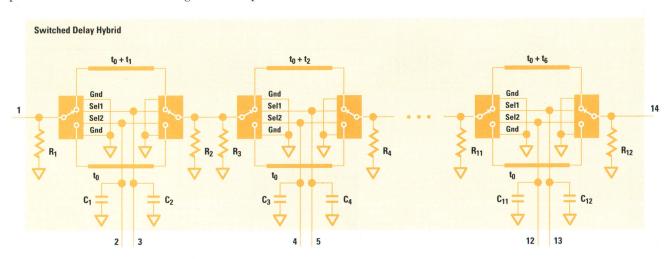

Filters. The  $\leq$  55-dBc harmonic performance of the instrument is achieved with a switched low-pass filter assembly. Six filters connected between two 1P6T (one-pole, 6-throw) p-i-n diode switches strip the harmonics from signals between 1 GHz and 20 GHz. The output combining switch also includes an extra throw for 0.01 to 1 GHz, making it a 1P7T switch. Harmonic filtering is not done for this path. The p-i-n diode used for this throw is a 1- $\mu$ s-lifetime diode, which maintains the harmonic performance down to 0.01 GHz. Fig. 15 shows typical second-harmonic performance; higher-harmonic performance is typically better.

The low-pass filters are distributed quasi-elliptic low-pass filters. They were computer optimized, emphasizing above-band spurious response. The lower three filters are asymmetric, which gives almost double the number of distinct transmission zeros in the stop band, and they are cascaded with five-element, higher-frequency, distributed low-pass filters to reduce spurious transmission bands.

**Fig. 15.** Typical second-harmonic levels measured at an output power of +6 dBm.

The next two filters are optimized, symmetric, distributed Chebyshev low-pass filters. The last filter is only four shunt stubs on a 50-ohm line. This makes its loss lower, and it is easy to cut off the stubs to create a 50-ohm through line. The filter cutoff frequencies are 1.65 GHz, 2.75 GHz, 4.80 GHz, 8 GHz, 12.8 GHz, and 21 GHz.

**Switches.** The p-i-n switches are compensated to match the off diodes' capacitance. The input splitting switch has four series-series arms and two series-shunt-shunt arms, the latter for isolation and low loss at higher frequencies. The output combining switch has six series-shunt arms and a 0.01-to-1-GHz arm farther down the line. In the 0.01-to-1-GHz arm, the long-lifetime p-i-n diode's capacitance serves as the middle element of a five-element distributed low-pass filter.

The bias elements are distributed where possible for low cost, and all have capacitive feedthroughs to connect to a standard printed circuit board for bias switching circuitry.

An example will illustrate the operation of the switches (see Fig. 10). Consider the operation at 2 GHz. Only the LPF2 path is biased on and all other paths are biased off. This is accomplished by the application of +15V to J18 and a negative current for J4, J5, J12 through J14, and J24. J10 and J11 are each connected to 330 ohms to ground. The +15V on J18 forward biases CR4, CR21, and CR22, the current being set by the voltage and the 330-ohm resistors. CR10 is reverse biased by this same +15V, and the path through LPF2 is established. The other paths' negative currents forward bias CR2, CR9, CR11 through CR16, CR18, and CR19. This also sets up a reverse bias on CR1, CR3, CR5 through CR8, CR17, CR20, and CR23 through CR28. Thus the signal can only flow through LPF2. An important consideration is that the low-pass filters that are off do not disturb the match. For this reason series-only diode switches can't be used. For example, if CR9 were not present, LPF1's output reflection coefficient, which has magnitude unity and arbitrary phase because of the line lengths required to connect the circuit, could resonate with the capacitance of reverse biased CR3 to make a short circuit at the output switch's common pole. The input switch uses series-series diodes to combat the same effect, which works only because of the finite Q of the reverse biased diode's capacitance.

## **Low-Band Output Section**

The low-band section (Fig. 16) provides the 10-MHz-to-1-GHz frequency band by dividing the 500-MHz-to-1024-GHz signal produced by the divide-by-four circuits in the output

Fig. 16. Block diagram of the low-band output section, which provides 10-MHz-to-1 GHz frequency coverage.

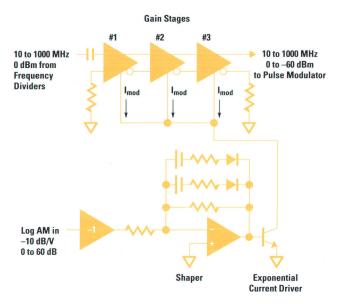

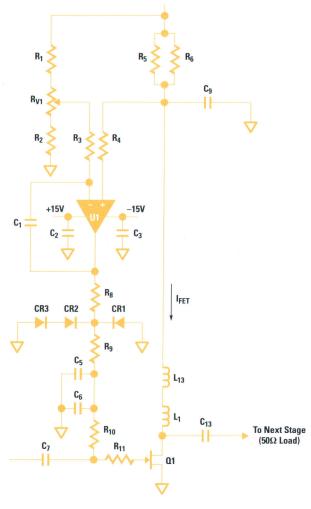

module microcircuit. The low-band input signal is divided, amplified, filtered to reduce harmonics, and detected for automatic level control (ALC). For modulated signal generator models, logarithmic AM and pulse modulators are inserted between the divider output and the amplifier input. The –55-dBc harmonic requirement inspired placement of filters at the end of the signal chain, easing the linearity constraint on the circuit blocks preceding the filters.

To minimize the impact on the cost of the 1-GHz-to-20-GHz base model, a modular design approach was taken. The low-band system consists of self-contained CW, modulation, and directional bridge detector printed circuit boards. Leveling is accomplished by ALC detection and drive signals with characteristics similar to the microwave system, allowing common use of the ALC circuits. This results in a system to which either a CW or a modulated frequency extension can be added without affecting the 1-GHz-to-20-GHz band.

**Dividers.** The divider block consists of a through path for the 500-MHz-to-1-GHz signal from the microwave output module microcircuit and six cascaded divide-by-2 stages to develop

the full 10-MHz-to-1-GHz band. A broadband limiting amplifier is used to sum all seven octaves of divider outputs. The limiter's output is a 0-dBm square wave with good match. Power level at this point is relatively independent of divider drive levels. Because of the performance limitations of the dividers above 300 MHz and the finite bandwidth of the limiter, second harmonics are as high as -12 dBc. Third harmonics reach the -9.5 dBc level predicted by analysis of a square wave.

**Output Amplifier.** One output amplifier covers the entire 10-MHz-to-1-GHz band. It consists of four cascaded gain stages with a p-i-n diode modulator between the first two stages. The 25-dB-gain amplifier provides a minimum power of +24 dBm. A 40-dB-dynamic-range p-i-n diode modulator is used for ALC. For a stable ALC loop bandwidth over all power levels, a constant dB/volt transfer function is desired. A shaped exponential current driver ensures a 3-dB/volt drive characteristic that closely matches that of the microwave system.

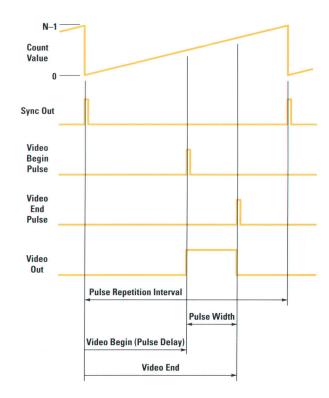

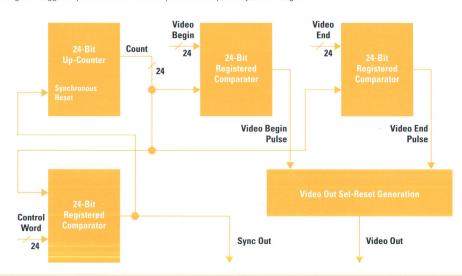

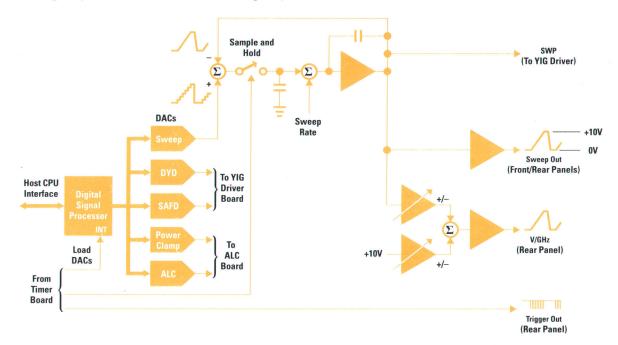

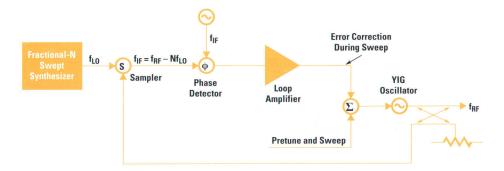

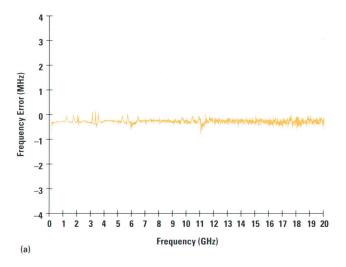

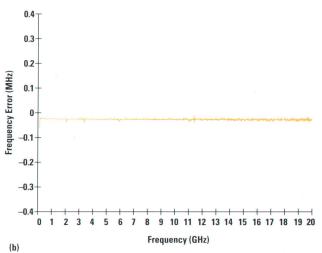

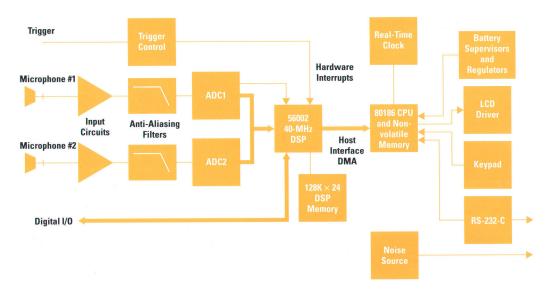

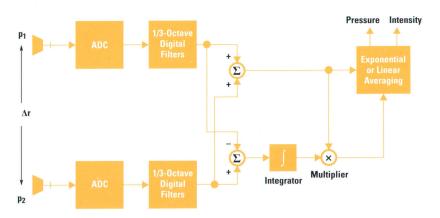

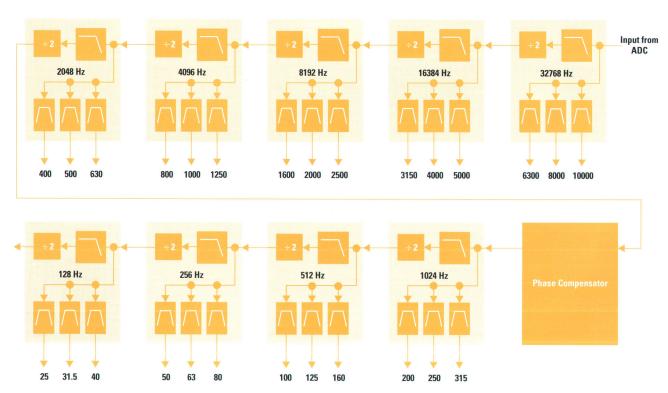

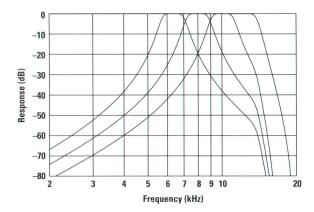

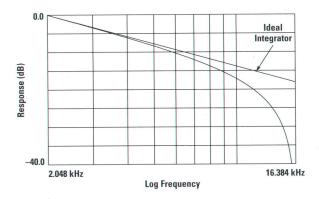

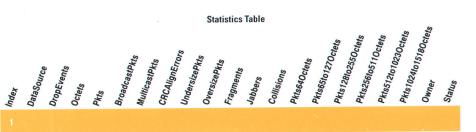

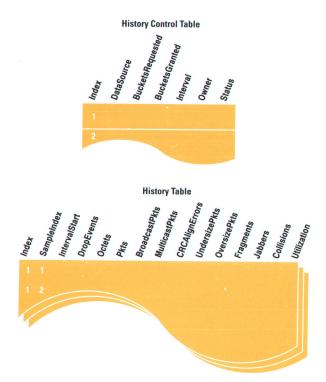

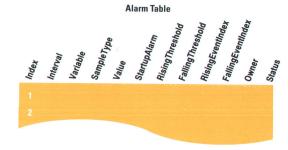

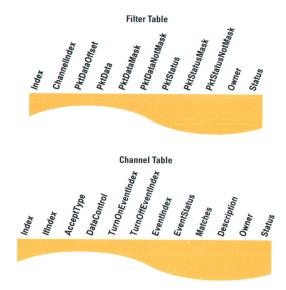

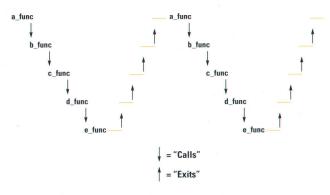

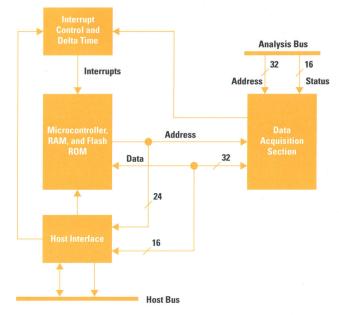

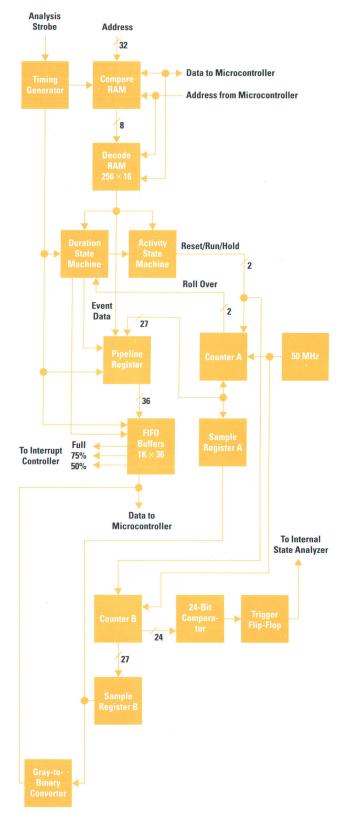

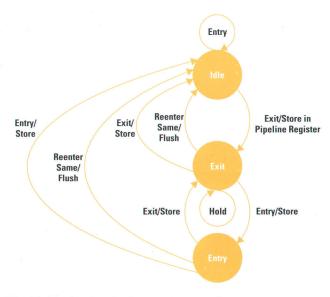

Fig. 17. Low-band logarithmic AM modulator.